OSBORNE/McGraw-Hill

# CRT Controller Handbook

TK7895 C3 K36

ry Kane

A stand alone reference book which can also be used as a supplement to An Introduction to Microcomputers: Volume 3 — Some Real Support Devices.

TK7895 C3 K36

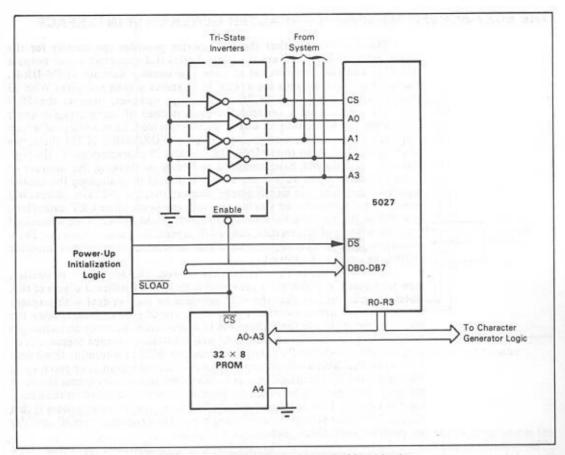

## The CRT Controller Handbook

277078

Gerry Kane

OSBORNE/McGraw-Hill Berkeley, California This book may be used to update Section H of An Introduction to Microcomputers: Volume 3 — Some Real Support Devices, Osborne/McGraw-Hill, 1978.

Published by OSBORNE/McGraw-Hill 630 Bancroft Way Berkeley, California 94710 U. S. A.

For information on translations and book distributors outside of the U. S. A., please write OSBORNE/McGraw-Hill at the above address.

#### THE CRT CONTROLLER HANDBOOK

Copyright © 1980 McGraw-Hill, Inc. All rights reserved. Printed in the United States of America. No part of this publication may be reproduced, stored in a retrieval system, or transmitted in any form or by any means, electronic, mechanical, photocopying, recording or otherwise without the prior written permission of the publishers.

234567890 CPCP 8987654321

ISBN 0-931988-45-4

Technical reviews by: William Houghton, Intel Corporation; Richard Palm, Synertek Incorporated; Vincent Rende, Standard Microsystems Corporation; Charles Carinalli, National Semiconductor.

Technical edit by Patrick McGuire, Leland Research. Cover design by Marc Miyashiro.

### Contents

## 1. CRT Principles of Operation

The Cathode Ray Tube 1-1

The CRT Controller-CRT Monitor Interface 1-8

CRT Character Generator Logic 1-8

Screen Memory 1-13

Manipulation of CRT Screen Data 1-16

The CRT Timing Chain 1-26

Graphic Versus Alphanumeric Displays 1-33

Comparing CRT Controller Devices 1-35

#### 2. DP8350 CRT Controllers

CRT Controllers Series Pins and Signals 2-3

Programmable Registers 2-8

CRT Controller-Microprocessor Interface 2-14

The CRT Controller-Screen Memory Interface 2-15

CRT Monitor Interface Signals 2-21

Mask-Programming Options 2-23

Data Sheets 2-31

#### 3. The 8275 CRT Controller

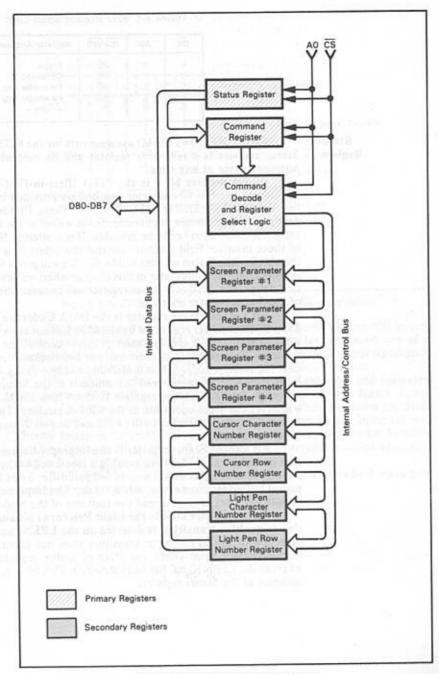

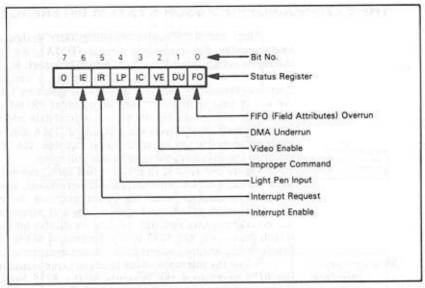

The 8275 CRT Controller Pins and Signals 3-3

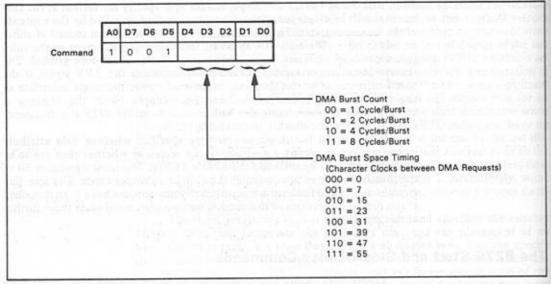

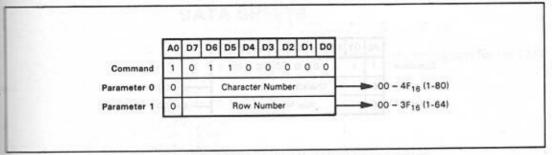

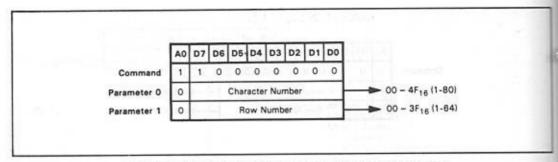

The 8275 CRT Controller Programmable Registers 3-6

The 8275-Microprocessor System Interface 3-10

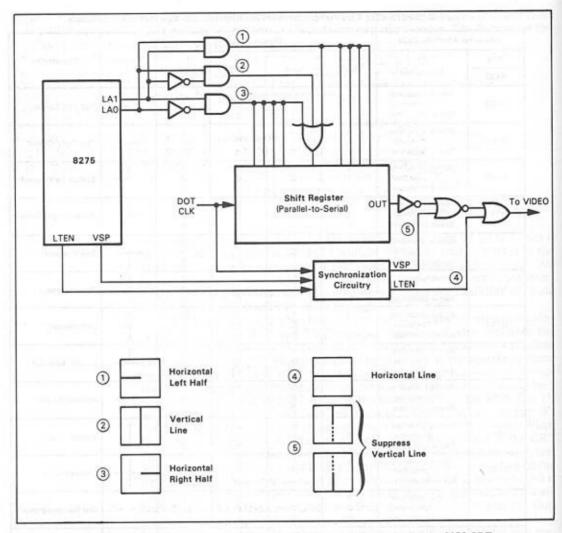

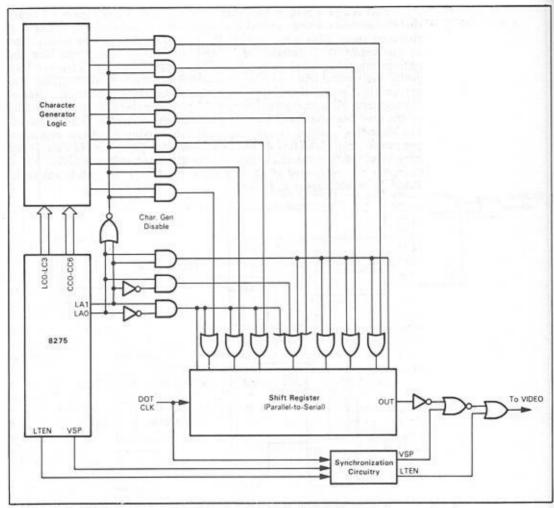

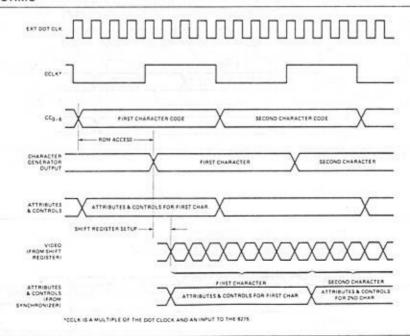

The 8275-Character Generator Interface 3-18

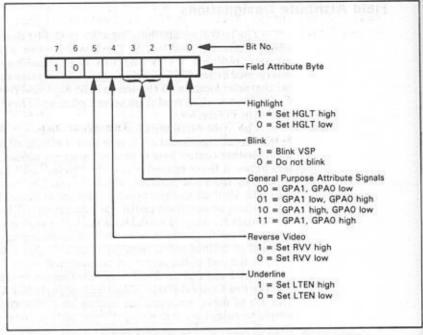

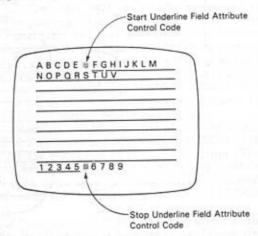

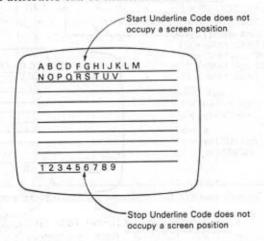

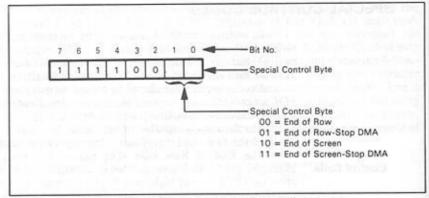

Special Control Codes 3-29

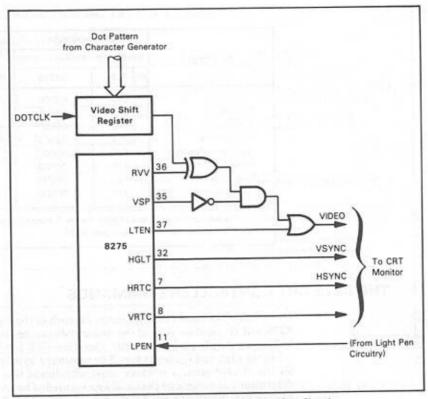

The 8275 CRT Monitor Interface 3-30

The 8275 CRT Controller Commands 3-32

Data Sheets 3-39

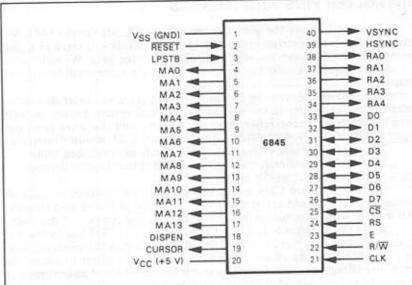

4. The 6845 CRT Controller

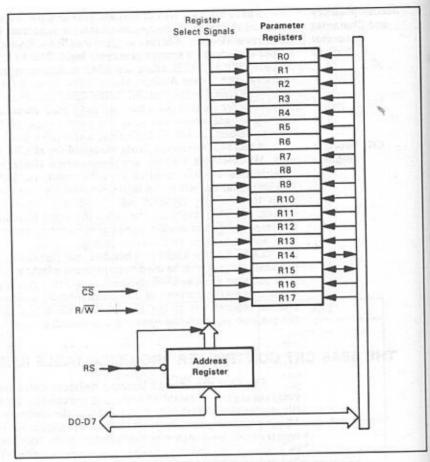

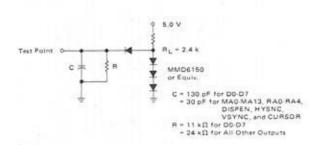

The 6845 CRT Controller Pins and Signals 4-3

The 6845 CRT Controller Programmable Registers 4-5

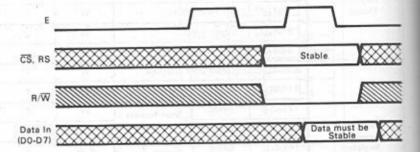

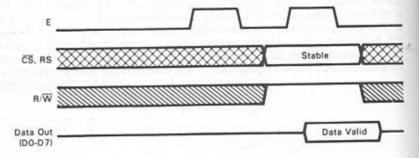

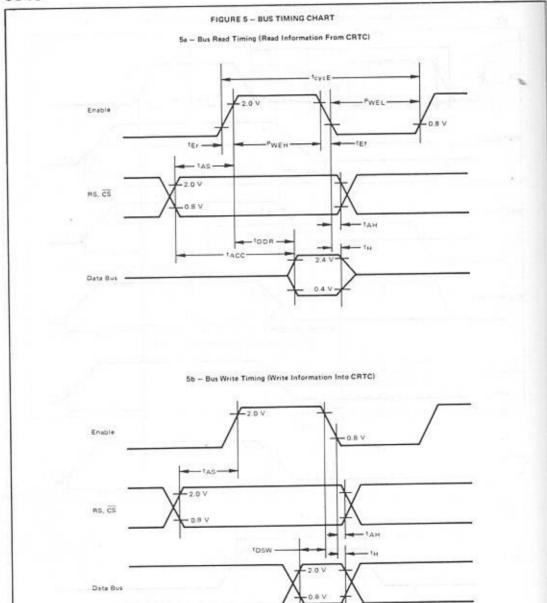

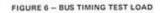

The 6845 CRT Controller-Microprocessor System Interface 4-8

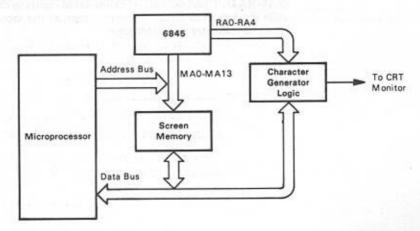

The 6845 CRT Controller-Screen Memory/Character Generator

Interface 4-9

The 6845 CRT Controller-CRT Monitor Interface 4-17

Programming the 6845 CRT Controller Registers 4-19

Data Sheets 4-31

5. The 6545 CRT Controller

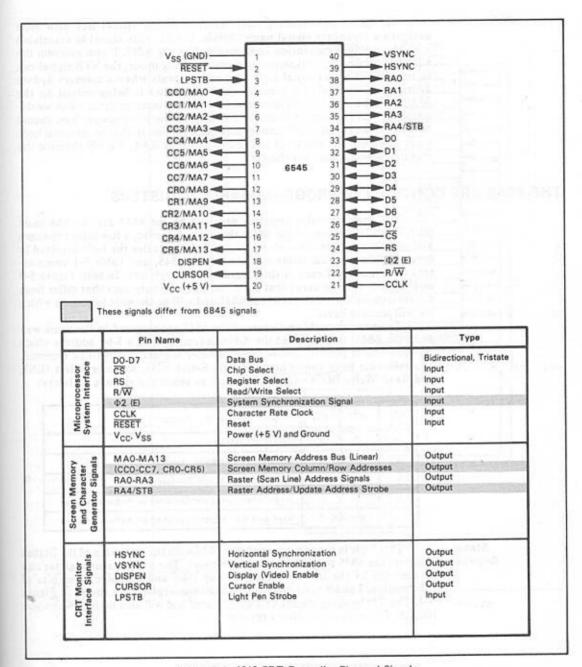

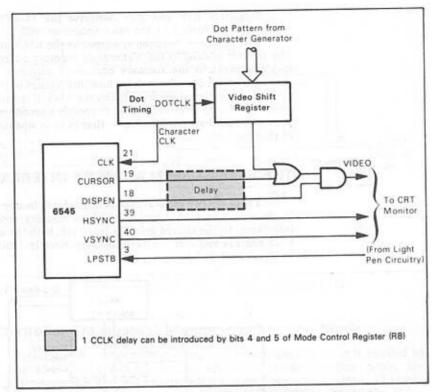

The 6545 CRT Controller Pins and Signals 5-2

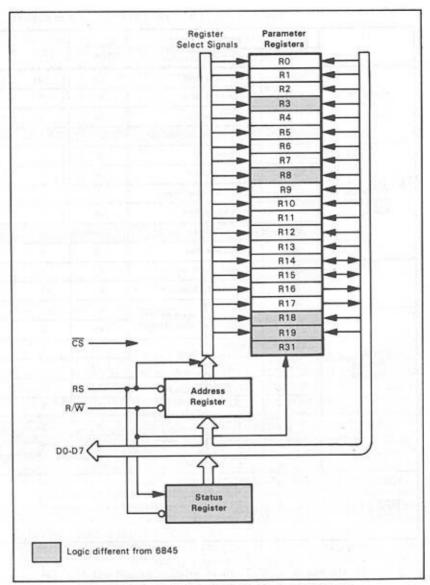

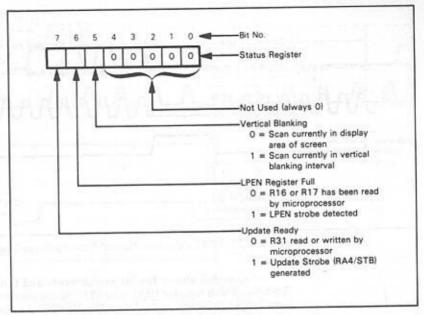

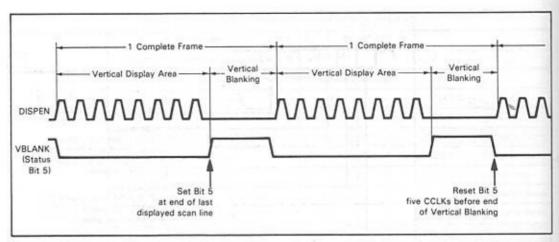

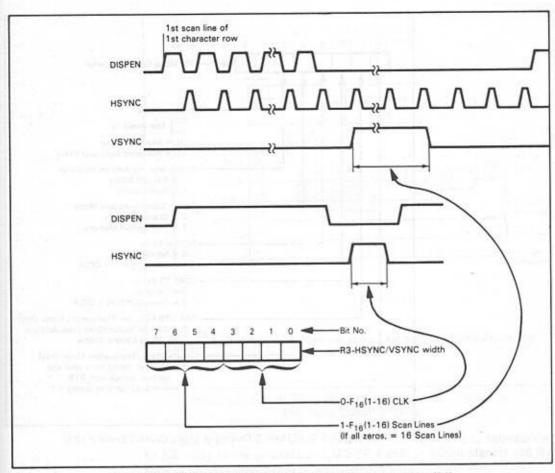

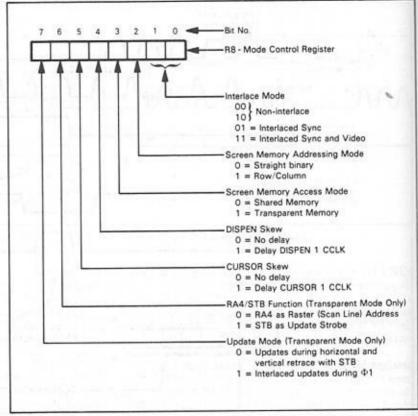

The 6545 CRT Controller Programmable Registers 5-4

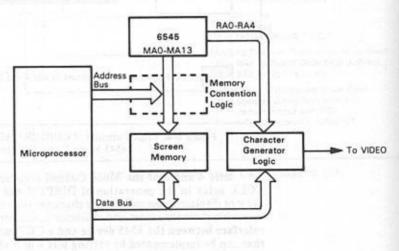

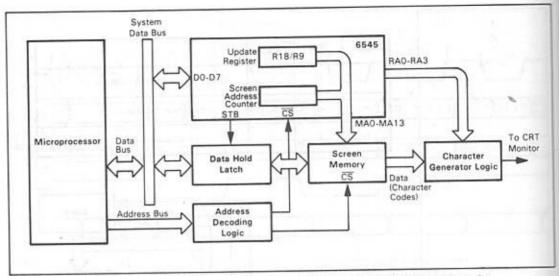

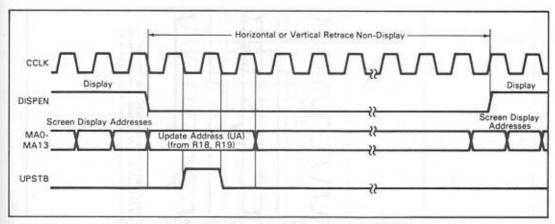

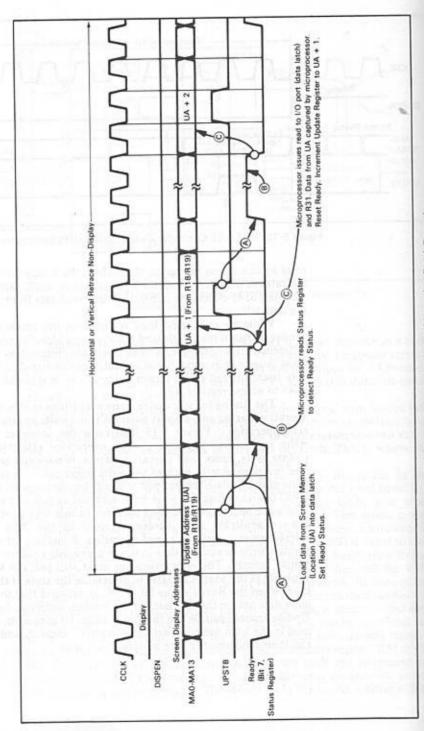

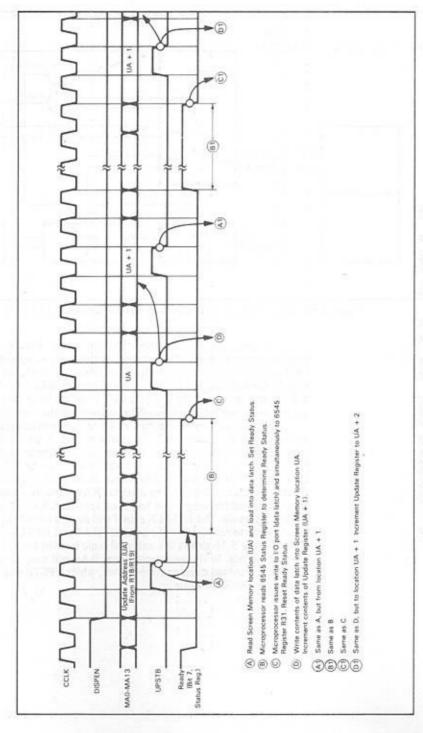

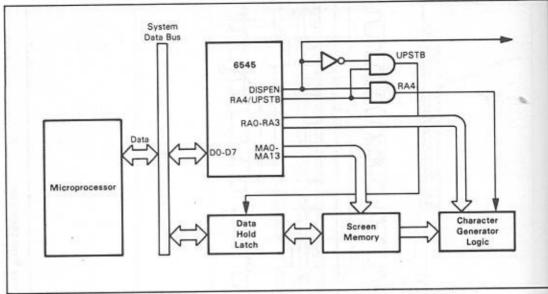

The 6545 CRT Controller-Screen Memory Interface 5-12

Data Sheets 5-23

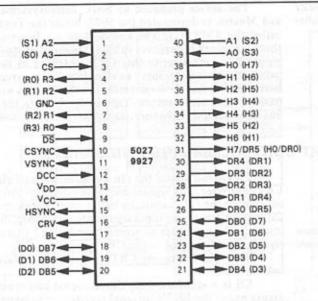

6. The 5027 CRT Controller

The 5027 CRT Controller Pins and Signals 6-3

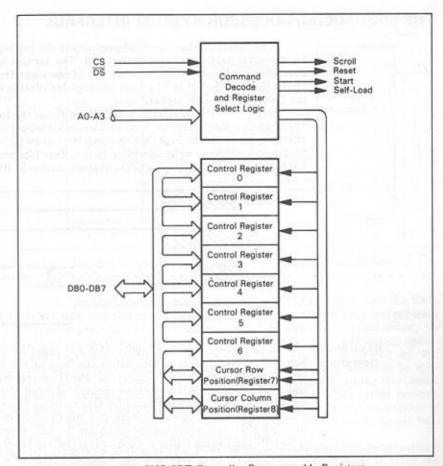

The 5027 CRT Controller Programmable Registers 6-6

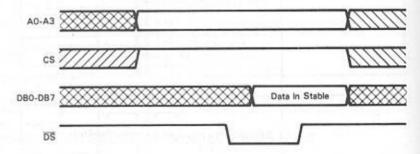

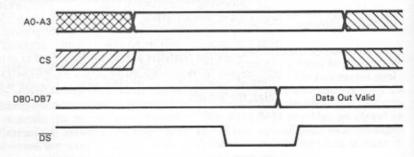

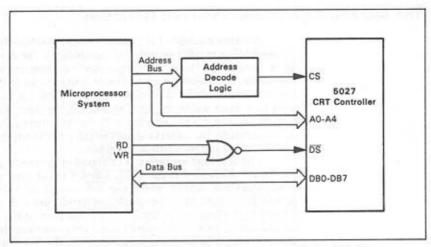

The 5027-Microprocessor System Interface 6-8

The 5027-Screen Memory/Character Generator Interface

The 5027-CRT Monitor Interface 6-13

Programming the 5027 CRT Controller Registers 6-15

The 5027 CRT Controller Commands 6-22

The CRT Controller Timing Chain 6-23

Data Sheets 6-25

## CRT Principles of Operation

Cathode ray tubes (CRTs) are ubiquitous devices. Most homes have several in the form of TV sets, and CRT-based terminals are used widely in both data processing and word processing computer systems. The widespread and ever increasing use of CRTs in computer terminals has led semiconductor manufacturers to design large-scale-integrated (LSI) devices to simplify and reduce the costs of control functions for CRT-based terminals.

In this book we will describe a number of LSI CRT controller devices. Although there are significant differences between the functions, capabilities, and characteristics of each of these CRT controllers, all of them have been shaped by the requirements of the cathode ray tube itself and by prevailing interface standards to this device. In this chapter we will discuss general principles of operation for the CRT and those terms and definitions which apply to all of the CRT controllers we will describe.

#### THE CATHODE RAY TUBE

The theory of operation of the cathode ray tube is described in great detail in numerous texts. Therefore, our description here will be quite simple; we will concern ourselves only with the general aspects of the theory which you should know in order to understand the interface between a CRT and its controller.

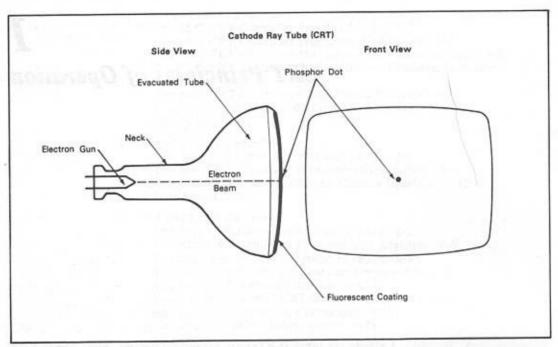

Figure 1-1 is a simplified representation of a CRT. A cathode ray tube is an evacuated glass tube which has a fluorescent coating on the inner surface of its rectangular frontal region (screen). An electron gun positioned at the end of the narrow cylindrical part of the tube (the neck) emits an electron beam. This stream of electrons strikes the fluorescent inner surface of the screen to produce an illuminated phosphor dot.

Figure 1-1. Simplified Representation of a Cathode Ray Tube (CRT)

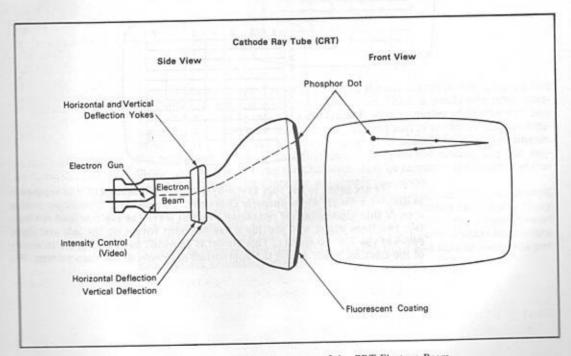

You can control the point at which the electron beam strikes the screen, and therefore the position of the dot upon the screen, by deflecting the electron beam. There are two primary methods of performing this beam deflection: electromagnetic and electrostatic. Electromagnetic deflection is by far the more common method and is used in all conventional television sets. Separate deflection coils are provided along the horizontal and vertical axes of the CRT neck. Separate signals can then be applied to effect horizontal and vertical deflection of the electron beam and thus move it across the surface of the screen. This operation is illustrated in Figure 1-2.

Persistence

As the beam is moved across the screen, it leaves a trace which takes some finite amount of time to dissipate. The duration of this trace depends on the characteristics of the fluorescent coating applied to the inner surface of the screen. This characteristic is called the "persistence" of the phosphor.

The horizontal deflection signal applied to the deflection coils affects only the horizontal position of the illuminated dot; likewise, the vertical deflection signal affects only its vertical position. Some CRT displays allow the user to arbitrarily position the dot by providing a horizontal and vertical input. With this type of display, the dot position is proportional to the linear voltages applied to these two inputs. This type of display is often referred to as a graphic, X-Y, or vector CRT display.

#### Raster Scan

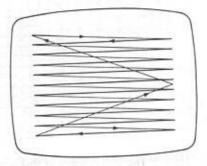

The far more prevalent type of CRT display is called a raster scan type. This type is used in all modern commercial television sets and in most CRT terminals designed for the display of alphanumeric data. In this type of display, the horizontal and vertical deflection signals are generated to move the beam in a raster or "rake-like" pattern that can be illustrated as follows:

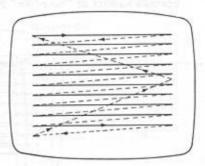

The raster scan pattern that we have illustrated still does not provide any method for displaying useful information on the CRT screen; so far, all we've done is produce a rake-like pattern on the screen. The first step towards making the screen useful is to eliminate the retrace portion of the raster scan pattern. This can be done by reducing the intensity of the electron beam during the retrace portion, using the intensity control for video input to the CRT illustrated in Figure 1-2. If the intensity of the electron beam is sufficiently reduced during retrace, then the flourescent coating on the screen

Figure 1-2. Controlling the Movement of the CRT Electron Beam

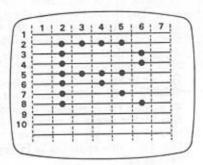

will not be sufficiently excited to produce an illuminated trace. The resultant pattern on the screen can be illustrated as follows:

The dotted lines in this illustration represent the retrace portion of the raster scan pattern when the electron beam intensity is reduced. The dotted lines would not be visible to a viewer. Now we have a series of approximately 10 horizontal lines or traces that are continuously displayed on the screen. While this is some improvement over the zigzag pattern that included retrace lines, we are still not displaying any useful information.

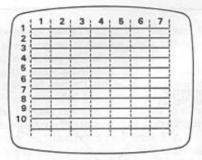

To see how information can be displayed on the screen, let us arbitrarily define our screen as having 10 horizontal traces or lines, and then let us divide each of those lines into seven segments. The resultant display could be represented as follows:

We are going to use this seven-by-ten  $(7 \times 10)$  matrix of line segments to display a single alphanumeric character. To provide a separation border around this alphanumeric character, we will leave the top line and the bottom two lines blank and provide a one-segment border on the left and right edges of the  $7 \times 10$  matrix. This border is provided by reducing the intensity of the electron beam during the appropriate segments of the scan pattern. We

will then be left with a  $5 \times 7$  matrix of line segments or dots in the center of our field:

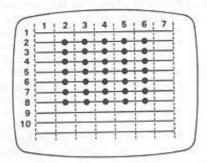

We can now represent alphanumeric characters within this  $5 \times 7$  matrix by reducing the intensity of the electron beam during the appropriate line segments. For example, the letter "R" can be represented as follows:

The beam intensity is reduced during the entire scan of line 1, during line segments 1, 6 and 7 of scan line 2, and so on. Thus, it would take seven consecutive scan lines to represent the letter R with a number of illuminated line segments or dots on each scan line representing part of the letter. Each illuminated dot will remain illuminated for some finite period of time depending on the persistence rating of the flourescent coating on the screen. The line segments or dots representing the character must be repeated or refreshed at frequent intervals, or the character will simply fade away.

In our discussion of the character formation using scan lines, we showed only ten horizontal lines. Obviously, a typical CRT screen can display many more lines than this, and each line will be subdivided into many more dots or segments than the few that we have illustrated. Let us now discuss the factors involved in determining the number of scan lines and dots or segments per line that are commonly used.

Horizontal and Vertical Scan Rates

In the United States, the horizontal sweep or scan rate of the electron beam for television is 15.75 kHz. If the beam is simultaneously moved vertically at a rate of 60 Hz, then 262.5 (15,750 + 60) horizontal trace lines can be produced while the beam is moved from the top to the bottom of the screen. Of course, some time is required to accomplish the horizontal and vertical retrace operations. Thus, some of the scan lines are effectively lost while performing the vertical retrace. A typical video system might require 21 or 22 scan lines of time to perform the vertical retrace, leaving about 240 raster scan lines for display of data. If we used 10 scan lines to form each row of alphanumeric characters, we could get a total of 24 lines of characters on the screen.

The number of characters that you can display horizontally along one of the rows depends on the video frequency used; that is, the rate at which you modulate the intensity of the electron beam. For example, if the horizontal scan frequency is 15.75 kHz and you want to display 100 8-dot wide characters per line, you would need a video frequency of 12.6 MHz (15,750 × 8 × 100 = 12.6 MHz). In an actual system you would blank about 20% of these characters to allow for horizontal retrace time and side margins; and would thus have an 80-character per line display with this video frequency.

The number of lines of data that can be displayed on the screen can be increased in several ways. The most obvious way would be to increase the horizontal sweep frequency so that more horizontal scan lines are produced during vertical scan of the screen. For example, if we increased the horizontal scan frequency from 15.75 kHz to 18 kHz and kept the vertical frequency at 60 Hz, we would increase the number of horizontal scan lines from 252.5 to 300 (18,000 ÷ 60 = 300). However, increasing the horizontal frequency may mean that you must use nonstandard beam deflection components to achieve this higher sweep or scan rate. In addition, you must now also increase the video frequency if you still wish to attain the same number of characters per line. Thus this approach to increasing the number of data rows can be quite expensive.

Refresh Frequency

Another approach is to reduce the vertical scan frequency. For example, if you maintained the horizontal frequency at 15.75 kHz but decreased the vertical frequency from 60 Hz to 45 Hz, you would increase the number of horizontal scan lines from 262.5 to 350 (15,750  $\pm$  45 = 350). The main problem with this approach to increasing the number of scan lines is that if the vertical refresh rate is not synchronized with the CRT's power line frequency, the electron beam can be deflected by stray magnetic fields, especially those produced by nearby power transformers. This effect can cause raster jitters if the sources of magnetic interference are not adequately shielded. For this reason it is usually advisable to have the refresh frequency be the same as the power line frequency. Therefore, the refresh frequency used in the United States is usually 60 Hz, while in other countries where the power frequency is 50 Hz the refresh frequency for CRTs is usually 50 Hz.

#### Interlaced Scanning

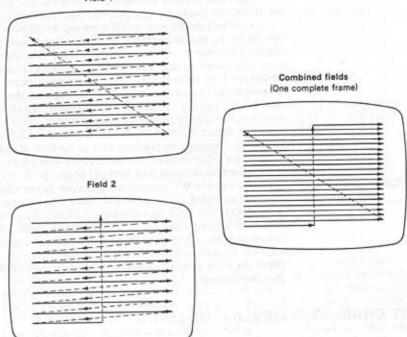

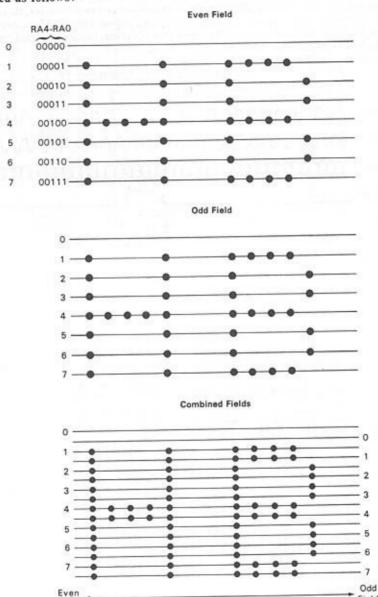

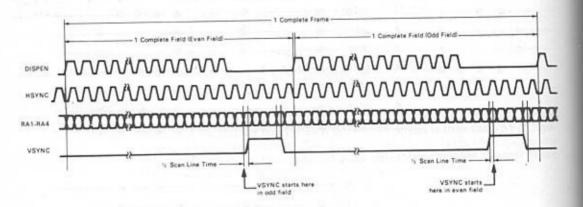

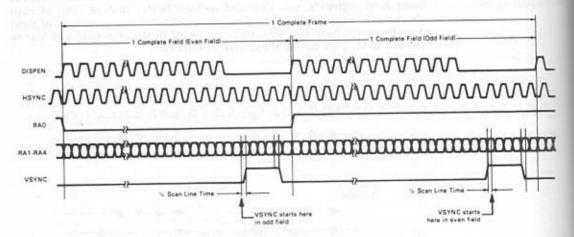

Another method of increasing the number of scan lines available for displaying data is to use a method known as interlaced scan. This is the scanning method used in broadcast television. In an interlaced scanning system, only half of the screen is refreshed during each vertical sweep cycle. Interlaced scanning can be illustrated as follows:

Field 1

An interlaced raster scanning system employs two sweep fields: when the electron beam reaches the middle of the first field's bottom line (line 262 in the illustration) it retraces not back to the top left corner, but rather to the middle of the top line where it is offset vertically by half a line. Thus the first line (line 263) of the second field is traced between the first two lines (lines 1 and 2) of the first field. The fields combine to make up one complete display frame.

One of the problems with this interlaced scan method is that you effectively halve the refresh rate: if the vertical sweep frequency is 60 Hz then a particular line on the screen will only be refreshed at a 30 Hz frequency. This 525 lines per frame, 262.5 lines per field interlaced scanning pattern we have just described is the system that is used in the United States for broadcast television. Since television scene content consists of large white areas, with adjacent fields being repeated, the low refresh rate provided in the interlaced scan method is quite acceptable. However, if you are using the CRT to display alphanumeric characters, all of the displayed data consists of small elements, and adjacent elements are not the same. In this application, an annoying flicker will usually result at a 30 Hz refresh rate unless a long persistence phosphor is used on the CRT screen.

#### THE CRT CONTROLLER-CRT MONITOR INTERFACE

A typical low-cost CRT monitor provides three signal connections to a CRT controller and associated electronics. The three signals are Horizontal Syncronization (HSYNC), Vertical Synchronization (VSYNC), and VIDEO. These signals are applied to the CRT monitor's electronics: the horizontal and vertical deflection control signals are then generated by the

monitor's electronics and applied to the tube itself.

The horizontal and vertical sweep oscillators of a CRT monitor are free running, and scanning is usually continuous; the purpose of the synchronization signals is not to start or stop the scan motion, but rather to shorten or lengthen the existing scan motions so that you can synchronize the presentation of information via the electron beam. The intensity of the electron beam is modulated by the video input to the CRT monitor. Commercial TV sets usually include video amplifier circuitry which can provid gray levels by properly regulating the beam intensity. In CRT monitors intended for display of alphanumeric data, however, simple on/off or black-white levels are all that are necessary to produce dots or no dots. Blanking levels are also fed to the video input to turn off the electron beam for the return trip or retrace on each horizontal scan and vertical frame scan.

Composite Video

On some CRT monitors, a single input signal called "composite video" is provided. The composite video signal includes HSYNC, VSYNC, and VIDEO. The CRT monitor then provides the circuitry to separate out the three signals comprising the composite video input. The major advantage of a composite video signal over three separate input signals is that this composite signal can be sent with a single coaxial cable. This is more convenient over long cable runs or in systems where the video display must be switched from one source to another.

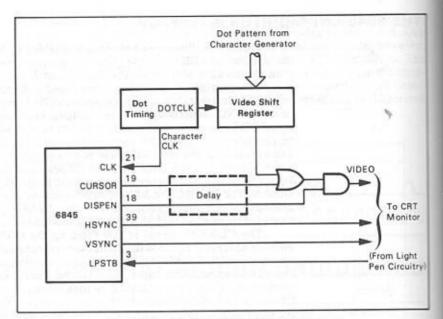

#### CRT CHARACTER GENERATOR LOGIC

In our preceding discussion of the CRT monitor, we briefly described how a single character can be created on the CRT screen. A series of dots is "painted" on the screen on successive scan lines to form a single character. The dot information is input to the CRT monitor serially on the VIDEO input. Obviously, some logic must be provided to convert data that is normally handled in 8-bit parallel bytes in a microcomputer system into the serial bit stream needed to create a corresponding data character on the CRT screen. In addition, since each character on the screen is represented by many dots, it will take more than eight bits of information to represent an alphanumeric character. Lastly, we will want to be able to write more than one character on a line; this implies that some sort of buffering will be required. Let us begin by seeing what would be needed to generate the characters for a single 80-character row on the CRT screen.

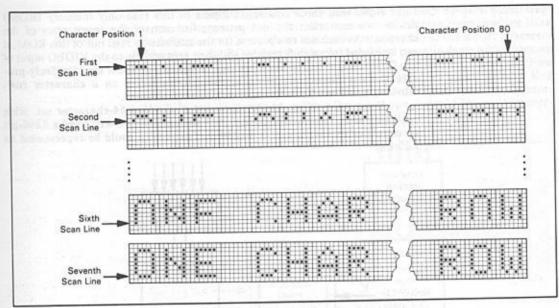

Figure 1-3 illustrates the sequence that occurs when displaying a single 80-character row of alphanumeric data on a CRT screen. First, the dot information for scan line 1 is applied via the VIDEO input to the CRT.

The dot pattern for all 80 characters on scan line 1 must be presented consecutively. When the first scan line is completed, the dot information for scan line 2 must be presented to the CRT. Once again, the dot information for all 80 characters must be applied consecutively. This sequence is repeated until all of the scan lines (seven in our illustration) for that character row have been

Figure 1-3. Display of One 80-Character Row of Data

completed. Thus dot information for each of the 80 characters on the character row must be presented to the CRT a total of seven times. The dot pattern presented for each character differs for every scan line. To see how the dot information for each character could be provided, let us examine the composition of a single character.

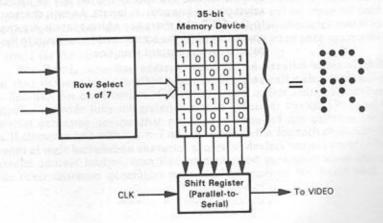

In Figure 1-3, each character is created in a  $5 \times 7$  matrix. Thus each character is actually represented by a total of 35 dots which can be either on or off. We could therefore store the pattern for a single character in a 35-bit memory device which could be represented as follows:

Now, with three row-select inputs to this read-only memory (ROM) device, we can select the dot patterns for each of the seven rows of the character. As each dot row pattern for the character is read out of this ROM, it can be loaded into a shift register and then sent serially to the VIDEO input of the CRT. That takes care of one character, but we must consecutively provide the dot pattern for each of the 80 characters on a character row. Obviously, we need a larger memory storage element.

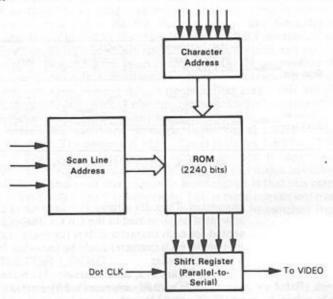

If we want to be able to represent a standard 64-character set, with each character represented by a  $5 \times 7$ -dot pattern, we will need a 2240-bit memory device ( $64 \times 7 \times 5 = 2240$ ). This device could be represented as follows:

We could now address the desired character in this ROM using six address inputs, and specify the dot row of that character using the three row select or scan line address inputs. As each character is required for presentation to the CRT, the character address inputs are changed to select the necessary character, while the scan line address inputs to the device access the correct dot pattern for the current scan line.

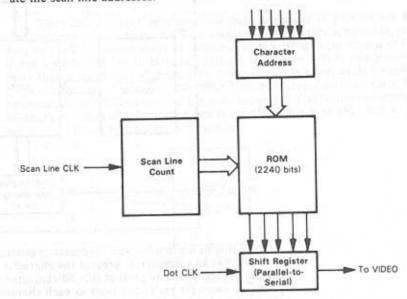

There are two problems with the simple approach we have illustrated: we are using an unnecessarily large number of address lines, and we have not defined a way in which we can consecutively present the proper character addresses to the ROM device. The first problem is easily dealt with: since we will always be accessing the scan lines in consecutive order (1 through 7) we can simply provide a scan line counter which will increment the scan line address (or dot row address) to the ROM as each CRT scan line is completed. In our illustrated example, a three-bit counter could be used to generate the scan line addresses:

Now the scan line address inputs to the ROM will remain constant for a complete scan line, while the character address inputs will be changed to address the dot pattern for each of the characters on an 80-character row. When a scan line is completed, the counter is incremented to select the next dot pattern row and the same 80-character sequence will be repeated until all seven rows have been scanned. When a subsequent 80-character row is to be presented to the CRT, the 3-bit row counter will be reset to once again address dot row 1 for the new character sequence.

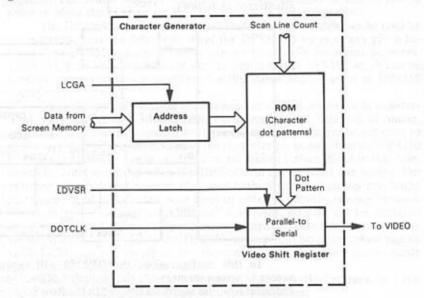

Character Generators

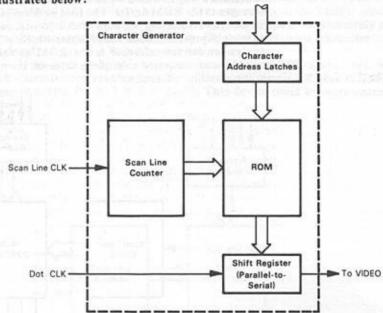

The ROM, scan line address counter, and parallel-to-serial shifter logic that we have just described comprise what we call a character generator. Because this combination of devices is used so frequently, a number of companies provide fully integrated character generator devices. You can get character generator devices that provide the required dot patterns for full ASCII character sets with a 5 × 7 or 7 × 9-dot matrix for each character. The amount of logic included on character generator devices varies: some include character address latches, scan line counters, and parallel-to-serial shifters, while other character generators may consist simply of the ROM with the required dot patterns stored in the device. For purposes of our discussion, we will define the character generator functions as including the elements illustrated below:

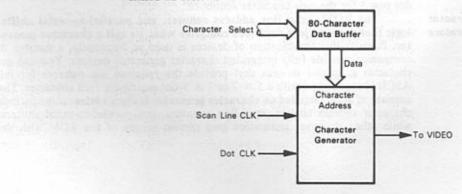

Now that we are familiar with the character generator functions, we must still find a way to successively present the character address inputs to the character generator and to present this 80-character sequence of addresses repetitively (once for each scan line) as each character row on the CRT is written. One simple scheme would be to construct an 80-character buffer which would be loaded with the data that is to be displayed. The characters in this buffer would then be accessed one after the other and presented to the character generator as each scan line is written to the CRT. The contents of this 80-character buffer would be accessed once for each scan line comprising a character row (seven times in our 5 × 7 matrix example). The relationship between the character row buffer and the character generator can be illustrated as follows:

One aspect of this relationship may not be obvious: the data word from the 80-character buffer is used as an address input to the character generator. Although the use of a data word as an address may seem a bit unusual, there is no reason why the bit pattern representing a character cannot be used as an address; each character has a unique bit pattern and thus presents a unique address to the character generator ROM.

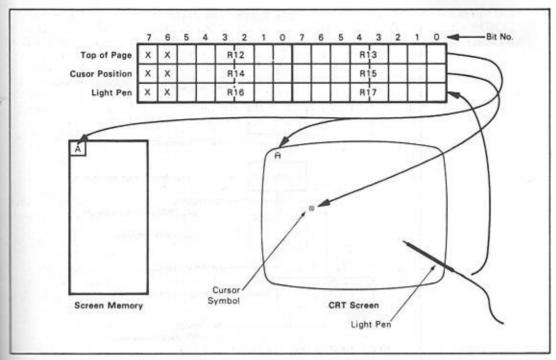

#### SCREEN MEMORY

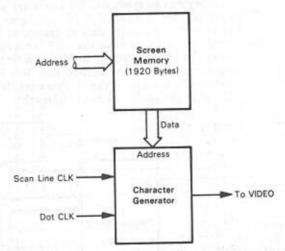

Thus far, we have developed the logic necessary to present one 80character row of data to the CRT for display. You will recall, however, that data on the CRT screen must be refreshed or rewritten to the screen at frequent intervals (50 or 60 Hz). In addition, the screen will be comprised of more than a single line of characters. One solution is to set aside an entire block of memory for storage of data that is to be displayed on the screen. For example, if our CRT screen is going to be capable of displaying twenty-four 80-character lines of information, we can assign a block of 1920 (80  $\times$  24) memory locations to store the screen data.

Screen Memory

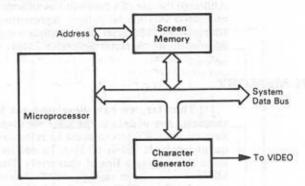

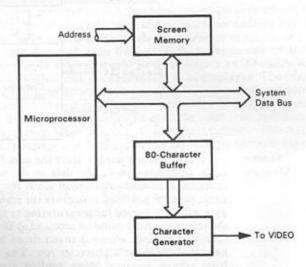

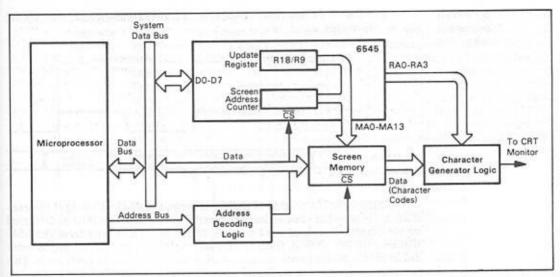

The memory used to store the data for display on the screen is referred to as screen memory. The data in the screen memory is presented to the character generator, which then sends the appropriate dot stream to the CRT. Logic must be provided to address the screen memory so that the appropriate data will be accessed for presentation to the character generator. The data in the screen memory could be accessed as 80-byte lines, with each of the twentyfour 80-byte lines accessed seven times in order to produce the seven scan lines that comprise a character row. The preceding illustration shows data from screen memory being applied directly to the character generator. However, we have not provided a path for putting data into screen memory; obviously, screen memory would not be read-only memory, since we want to be able to vary the data that is displayed on the CRT screen. Typically, screen memory would simply be connected to the system data bus as shown in the following illustration:

Now the microprocessor can load screen memory with data that is to be displayed on the CRT screen. Subsequently, the stored data in screen memory can be applied to the character generator as required to create the display. One problem with this arrangement is that the character generator requires that the same data be applied to it over and over again in order to create the dot stream for the CRT. This results in the system data bus being used almost continuously to pass data from screen memory to the character generator. Use of the system data bus for this purpose could be greatly reduced by combining the 80-character line buffer which we discussed earlier with the screen memory approach:

the

o be een the ator r to eing cter atly

ear-

A complete character row can now be loaded into this buffer from screen memory via the system data bus. The contents of the 80-character buffer will then be repeatedly presented to the character generator while the scan lines comprising a character row are being sent to the CRT screen. With this approach, the system data bus will be used by the CRT-related devices only when a new line of characters must be passed from screen memory into the line buffer. While use of the system data bus by CRT-related functions is still significant, the line buffer approach does help to alleviate traffic.

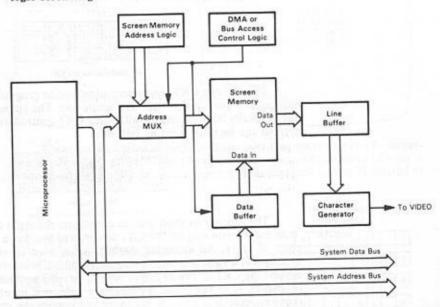

The preceding illustration still does not deal with the logic required to generate the addresses to access screen memory; this is one of the functions typically provided by a CRT controller. The following illustration includes a logic block to generate addresses for screen memory:

Since screen memory must also be accessed by the microprocessor, the preceding figure includes address multiplexing logic and data buffering logic. There are, however, a number of other techniques that might be used to provide for bus sharing by the CRT-related devices and the microprocessor. The method used in a particular system depends on the various system demands as well as on the characteristics of the CRT controller being used. For example, Intel's 8275 CRT controller usually requires the use of an external DMA controller in the system. Other CRT controllers provide some minimal bus access contention logic to simplify coordination of system bus sharing. Some CRT controllers provide no DMA or bus access contention logic, and you must provide all the necessary logic externally.

#### MANIPULATION OF CRT SCREEN DATA

Cursor

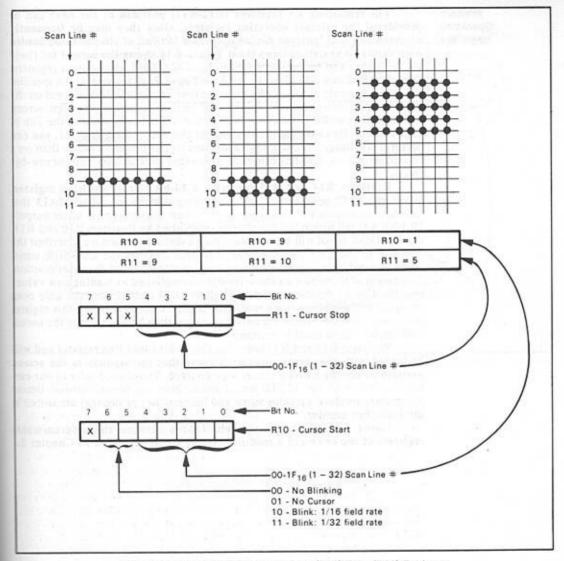

We have seen how a copy of the data that is to be displayed on a CRT screen is maintained in screen memory. When you want to change information that is displayed on the screen, you simply write the new information into screen memory at the appropriate location. When a CRT display is being used as part of a terminal, some method must be provided so that an operator can determine and control the location on the CRT screen where new data is to be entered. Therefore, all of the CRT controllers we will describe can generate and display a cursor on the screen. The cursor is simply a visible symbol that may be moved about the screen where a transaction is to take place. The cursor is typically displayed as a horizontal line below a character position:

Underscore cursor

Some of the CRT controllers allow you to program the cursor so that it appears as a block rather than as a single line. The cursor can also be made to automatically blink on and off with some CRT controllers. A block-type cursor symbol can be illustrated as follows:

Block cursor

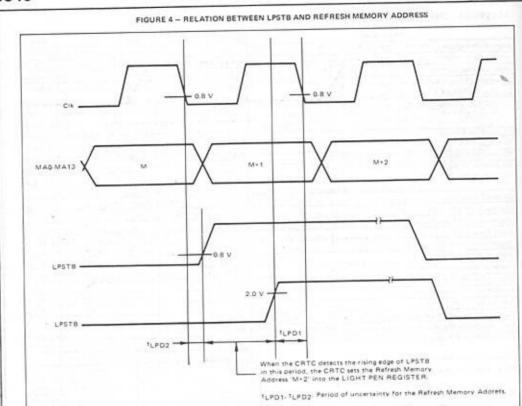

Light Pen Inputs The primary method used to coordinate the input of data by an operator to an appropriate spot on the CRT screen is to position a cursor to indicate the point of entry. An alternate method, often used in graphic-oriented CRT systems, is a light pen input. With this method, you simply hold the light pen against the CRT screen to physically indicate the position where a transaction or change is to occur. Implementing a light pen input into a CRT system requires additional external hardware and implies the presence of some additional logic. To understand what is required, let us briefly discuss how the light pen input works.

Light pens are actually light sensor devices. When you hold the light pen against the CRT screen, it will detect the passage of the CRT's electron beam in front of the pen, generating a pulse which is sent to the CRT controller. Since the CRT controller is generating all of the scan line and character counts for the CRT screen, it knows the position of the electron beam on the screen at any given moment. Thus, when it receives the signal from the light pen, the values from the controller's appropriate counting registers can be saved to record the position of the light pen.

Several of the CRT controller devices we will describe provide a light pen input. All of them simply use an internal register to store the appropriate counter values at the time when the light pen input signal is received. The microprocessor can then read the value stored in the register to determine the location of the light pen.

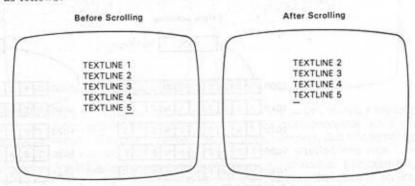

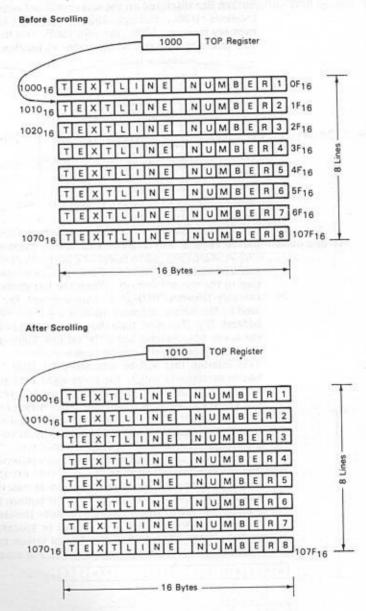

If the CRT screen is being used for entry of data or display of text, it is often desirable to make the screen appear as though it were a sheet of paper in a typewriter. Text is entered beginning at the top line of the screen and subsequent lines are entered below. When the bottom line of the screen is reached, the text on the screen is moved up, or scrolled. Scrolling on the screen causes the top line to be lost from view while creating a vacant bottom line for entry of additional data. This scrolling operation can be illustrated as follows:

There are a number of ways that the scrolling operation can be implemented. The most straightforward method from a conceptual point of view is to simply move the data in screen memory. This approach can be illustrated as follows:

| Before Scrolling       | After Scrolling        |

|------------------------|------------------------|

| 1000 TEXTLINE 1        | 1000 TEXTLINE 2        |

| 1010 TEXTLINE 2        | 1010 T E X T L I N E 3 |

| 1020 TEXTLINE 3        | 1020 T E X T L I N E 4 |

| 1030 TEXTLINE 4        | 1030 T E X T L I N E 5 |

| 1040 T E X T L I N E 5 | 1040                   |

There is a very obvious problem with this approach: moving all of the data around in screen memory requires an unacceptably large amount of time and attention from the microprocessor.

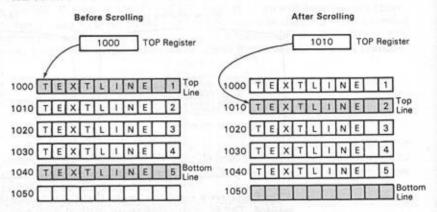

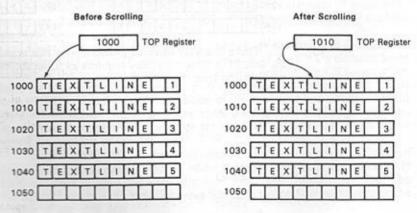

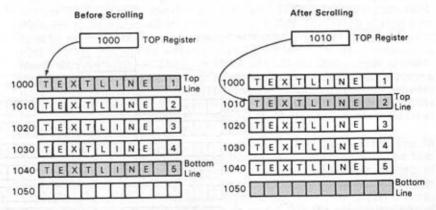

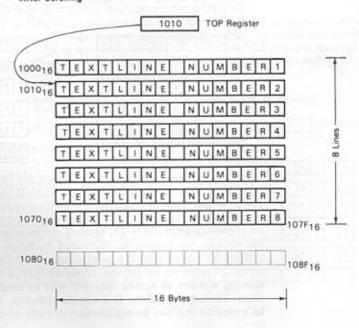

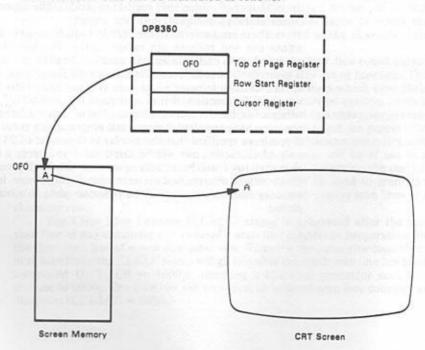

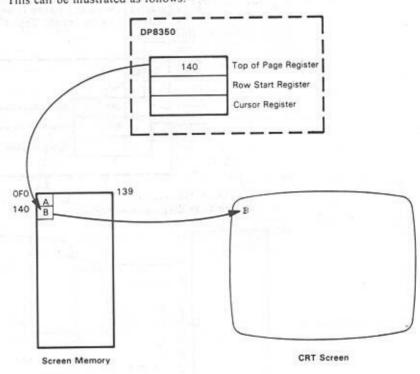

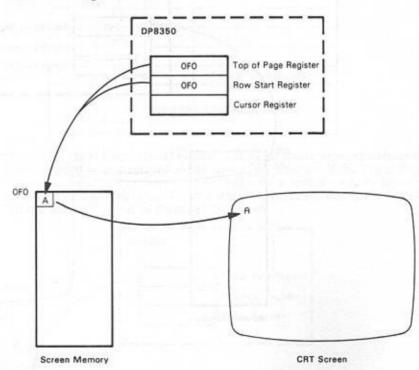

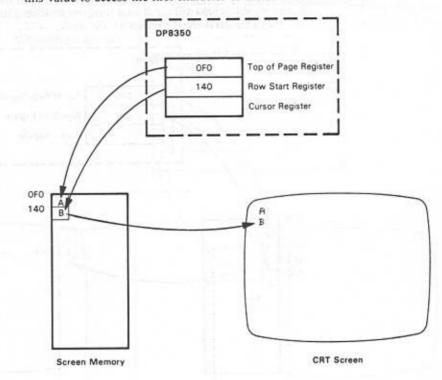

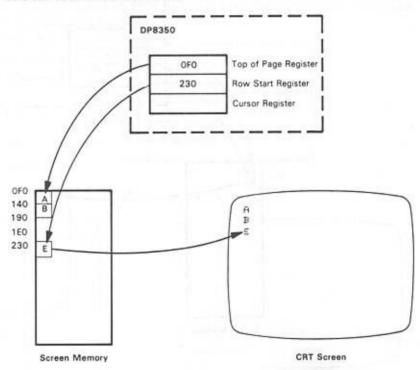

A much simpler method of performing the scrolling function is to maintain a register which will hold the screen memory address where the first line of displayed data begins. This address, which we will call TOP, would be used as the starting point when screen memory is accessed at the beginning of the first scan line on the screen. When the contents of the screen are to be scrolled upwards, the register holding the TOP address is incremented by a value corresponding to the number of characters contained in one line. This approach can be illustrated as follows:

With this approach, no actual movement of data is required. We have simply changed the starting location of screen memory and thus effectively moved the data that is displayed on the screen upward. Using this approach, you could also scroll downward since the previous top line (TEXTLINE 1) is still available in memory beginning at location 1000.

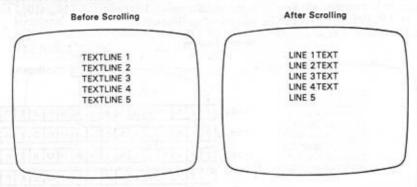

The scrolling operations we have thus far illustrated moved data one line at a time. There is no reason, however, why we could not scroll the screen data on a character-by-character basis if we desired. For example, we could scroll the screen data four characters upwards and to the left by adding 4 to the TOP register value as follows:

The display that would result from this type of character scrolling operation can be illustrated as follows:

Scrolling by manipulation of the contents of the screen memory starting address greatly reduces the burden placed on the microprocessor since no actual movement of data is required. You will note, however, that this scrolling technique still requires that memory locations being "scrolled into view" be cleared or loaded with the value representing a space character. For example, in the following line scrolling operation you must be sure that the ten screen memory locations beginning at location 1050 are cleared, since whatever is contained in those locations will be displayed as the bottom line on the screen after scrolling.

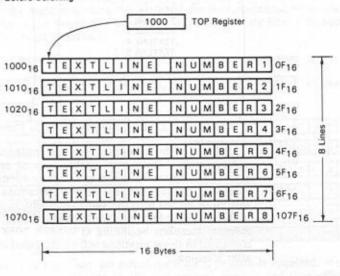

There is one obvious problem with the type of scrolling operation we have been illustrating. Each time we scroll, we effectively move a "window," whose size is equal to the display capacity of the screen, through memory. For example, if our screen displays 24 80-character lines, then we must provide 1920 (80 × 24) bytes of screen memory. Each time that we scroll the display, we require an additional 80 bytes of memory, as the starting address for screen memory is incremented by 80. After we have scrolled the screen 24 times we will have utilized 3840 (1920 × 2) memory locations. This moving window of screen memory will be unacceptable in many applications. Fortunately, there is a simple solution. To illustrate these solutions, let's assume that our screen consists of eight 16-character lines. We therefore

need 128 bytes of screen memory which we will position at addresses  $1000_{16}$  through  $107F_{16}$ . Now, when the entire screen is filled with text and we want to scroll the screen data upward, we must add  $16_{16}$  ( $10_{10}$ ) to the TOP register. This can be illustrated as follows:

Before Scrolling

After Scrolling

When the next scan of screen memory begins, it will now start with location 101016. Eight lines of text (128 characters) will be displayed; however, the bottom line displayed on the screen will not consist of the contents of memory locations 108016 through 108F16; instead, TEXTLINE NUMBER1 from memory locations 100016 through 100F16 will be displayed as the bottom line. The screen display can be illustrated as follows:

> TEXTLINE NUMBER 1 **TEXTLINE NUMBER 2** TEXTLINE NUMBER 3 TEXTLINE NUMBER 4 TEXTLINE NUMBER 5 TEXTLINE NUMBER 6 **TEXTLINE NUMBER 7** TEXTLINE NUMBER8

TEXTLINE NUMBER2 TEXTLINE NUMBER3 TEXTLINE NUMBER4 TEXTLINE NUMBERS TEXTLINE NUMBERS TEXTLINE NUMBER7 TEXTLINE NUMBER8 TEXTLINE NUMBER1

#### Memory Wraparound

This phenomenon is due to wraparound of screen memory. In our example we require only 128 bytes of screen memory. Only seven address lines (A0-A6) are required to select one of the 128 locations. Therefore, the screen memory addressing logic need only generate seven address signals for connection to the screen memory. When the last character in the last row of screen memory (location 107F16) is being accessed, the seven address signals generated by the screen memory address logic will all be set to 1 to represent the address 7F16. The next time the screen memory address logic is incremented, the seven address lines will all be set low. Since only these seven address lines need be applied to the screen memory to select one of the 128 locations, the next location that will be accessed after 107F16 will be the first location in screen memory (100016). The more significant address lines needed to represent the address 108016 are not connected to screen memory and are therefore not a factor in the screen function. They may, of course, be used in other ways within a system to select other memory or I/O devices, or as chip enable inputs to the screen memory devices, but these uses can be made transparent so far as the screen memory address logic is concerned.

There is still one problem with this wraparound technique of scrolling. In the example we just illustrated, all of the text has been moved up one line. However, since the last line of screen memory now effectively consists of memory locations 0016 through 0F16, the bottom line of the screen will display TEXTLINE NUMBER1. In order to have the last line of the display cleared, the microprocessor must write blanks or spaces into the appropriate line of screen memory. In addition, the line of screen memory that must be cleared will change with each scrolling operation. For example, after the bottom line of screen memory has been cleared and a new text line (TEXTLINE NUMBER9) has been entered, the following scrolling procedure would be performed:

Now the top of screen memory begins at address 102016, and it is the old TEXTLINE NUMBER2, which begins at screen memory location 101016, that must be cleared by the microprocessor to clear the bottom line displayed on the screen. This scrolling procedure obviously imposes some burden on the microprocessor to keep track of the current bottom line of display memory and clear that line as part of each scrolling operation. However, this wraparound approach to scrolling makes the screen memory address logic provided by a CRT controller quite straightforward. And, since it is this addressing logic which makes the majority of accesses to screen memory, it is important that this logic be kept simple.

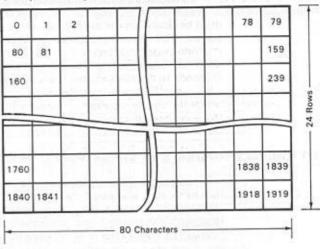

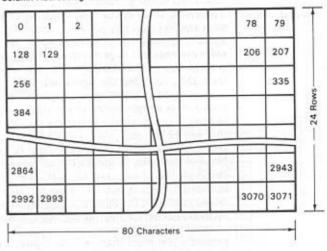

#### Screen Memory Addressing: Linear versus Row/Column

In our preceding discussion of screen memory addressing, we assumed that memory is addressed linearly; that is, the addressing is done as though all locations on the display were stored in a continuous string of memory locations. This is the way that microprocessors assume that memory is configured. This approach is not always the most efficient, however. For example, if you are manipulating the data that is displayed on a CRT screen, it is often most convenient and efficient if the data can be handled on a display line basis. This is especially true when you want to implement text editing functions such as insert line, delete line, and insert/delete character. Therefore, some of the CRT controllers provide screen memory addressing on a row/column basis. In this approach, some of the memory address lines specify the data row of the character. While this approach can simplify the software required to perform many data manipulation functions on the CRT screen, it is accomplished at the cost of memory usage efficiency. To illustrate this, consider the figure below.

As you can see, using standard linear addressing, the first character on each row is simply stored in the next consecutive memory location following the last character on the preceding row. If row/column addressing is used, then this will be the case only if the number of characters on a row equals some power of two. Otherwise, some memory locations will effectively be inaccessible. For example, in the illustration above, the last character on the first data row is at memory address 8010 while the first character on the next data row is at location 12810. The intervening memory addresses are not accessible. There are ways around the dilemma, such as using external logic or ROM to map the addresses generated by the microprocessor and those generated by the CRT controller for screen memory into the same address spaces. Thus, the tradeoffs you must make will be between more complicated software for text manipulation versus inefficient use of memory space and additional address mapping logic.

Linear (Binary) Addressing (Decimal addresses)

Row/Column Addressing (Decimal addresses)

#### Memory Contention Logic

Although there are a number of methods that can be used to resolve screen memory contention existing between the microprocessor and the CRT controller, there are three techniques that are most commonly used: direct memory access (DMA), interlaced memory access, and, for want of a better term, what we will call non-display-time access.

Direct Memory Access

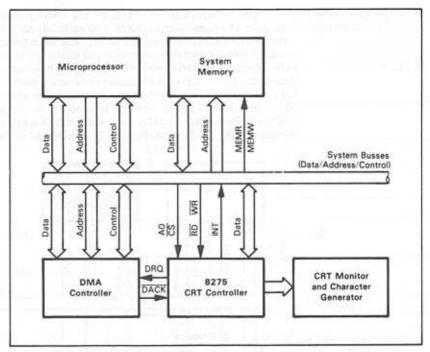

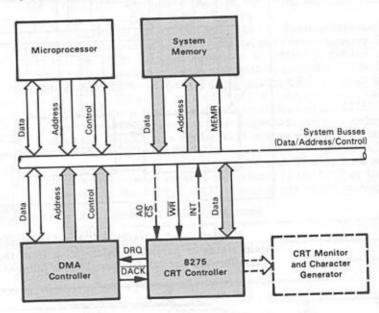

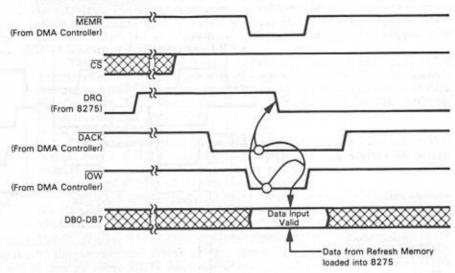

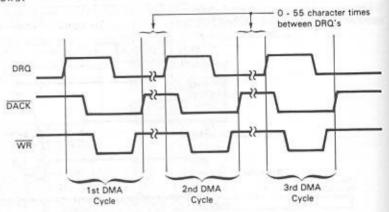

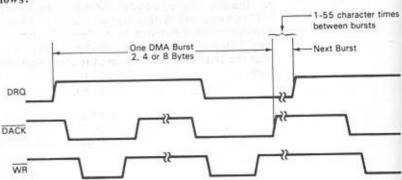

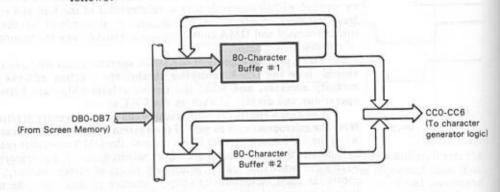

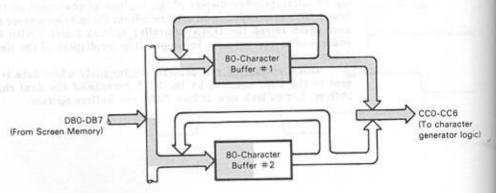

The DMA approach utilizes an external DMA controller to handle transfers of data between the microprocessor and screen memory, and between screen memory and the CRT controller. With this technique, the CRT controller will not always have access to screen memory. Instead, blocks of data, typically one character line, will be transferred under control of the DMA controller from screen memory to the CRT controller logic. This approach is the one used in the Intel 8275 CRT controller which provides two 80-character buffers to hold data from screen memory.

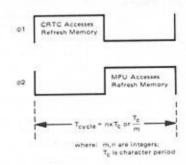

Interlaced Memory Access

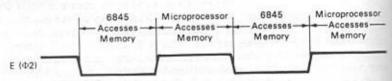

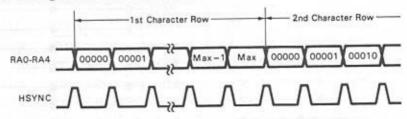

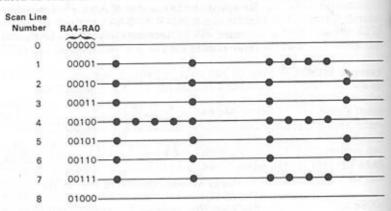

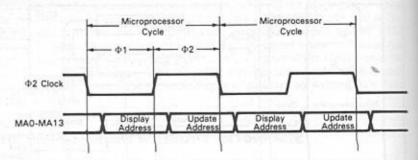

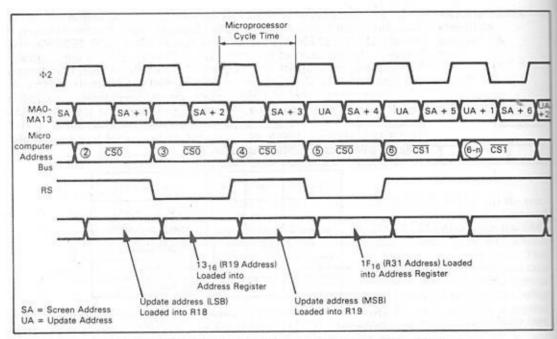

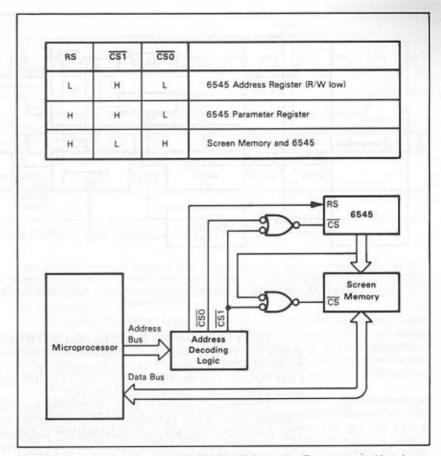

The interlaced memory technique assumes that the CRT controller and microprocessor will have equal and alternating periods of time when they can access screen memory. For example, the 6800 and 6500 families of microprocessors use two-phase clocks, and the microprocessor will only be using the system busses during one of the two phases. Therefore, the CRT controller can be guaranteed access to the busses during the alternate phases. We will discuss this technique in more detail when we describe the 6845 and 6545 CRT controllers.

Non-Display-Time Access

A third technique for resolving screen memory contention consists of granting the microprocessor access to screen memory during non-display times when the CRT controller logic does not need access. The amount of time that will be available to the microprocessor to access screen memory depends, of course, on your system design. For example, if the system does not include a line buffer between screen memory and the character generator, then the CRT controller will need almost continuous access to the screen memory. Even in this case, however, there are periods of time when screen memory can be accessed by the microprocessor. You will recall from our discussion of CRT timing that dot information for the alphanumeric character display must be presented during each horizontal scan line. However, no dot information need be presented during horizontal retrace or vertical retrace, and these time intervals can therefore be made available to the microprocessor to access screen memory. Typically, horizontal retrace represents approximately 20% of the horizontal scan line time; thus, 10-15 microseconds would be available to the microprocessor during each horizontal retrace operation. The vertical retrace time in a typical system would provide another 1-1.5 milliseconds at the end of each frame. Additionally, the contents of screen memory need not be applied to the character generator for every horizontal scan line: for example, a 5 × 7 dot matrix character might be centered in a 7 × 9 matrix. In this case, dot information would only be presented during seven of the nine scan lines which comprise a character row. Screen memory could therefore be made available to the microprocessor during the first and last scan lines of each character row.

Determining when screen memory can be accessed by the microprocessor will require some logic. However, this logic can be minimal since some of the useful signals such as vertical blanking and scan line counts will already be available in the system.

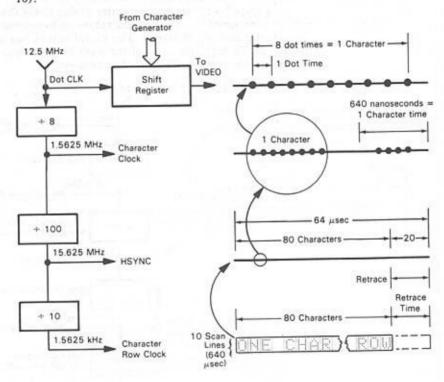

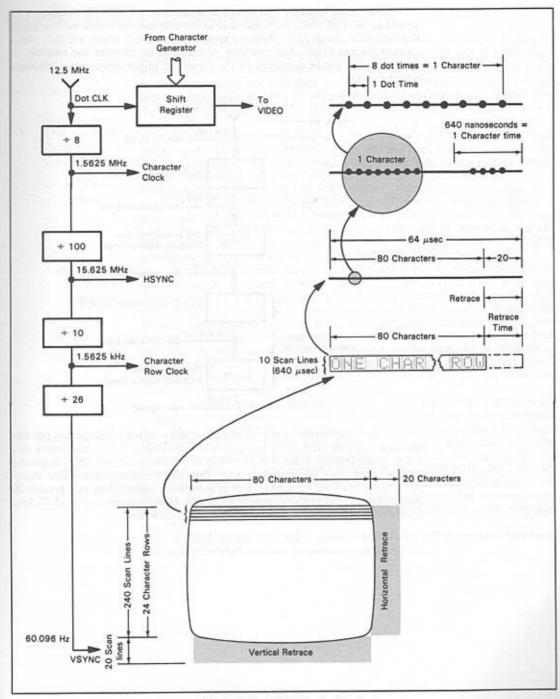

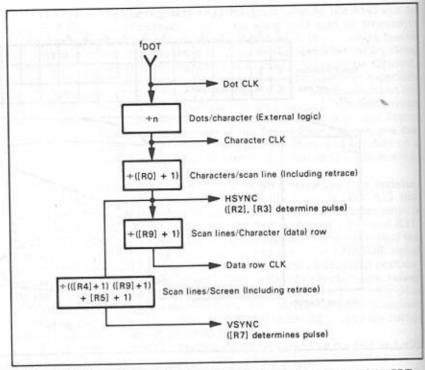

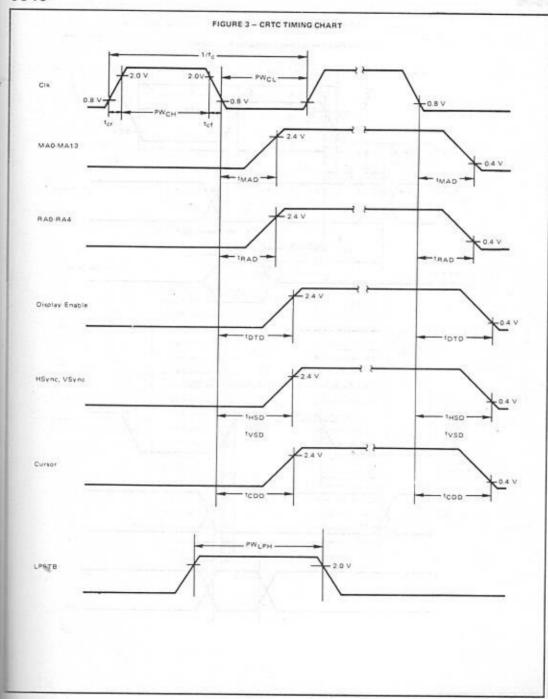

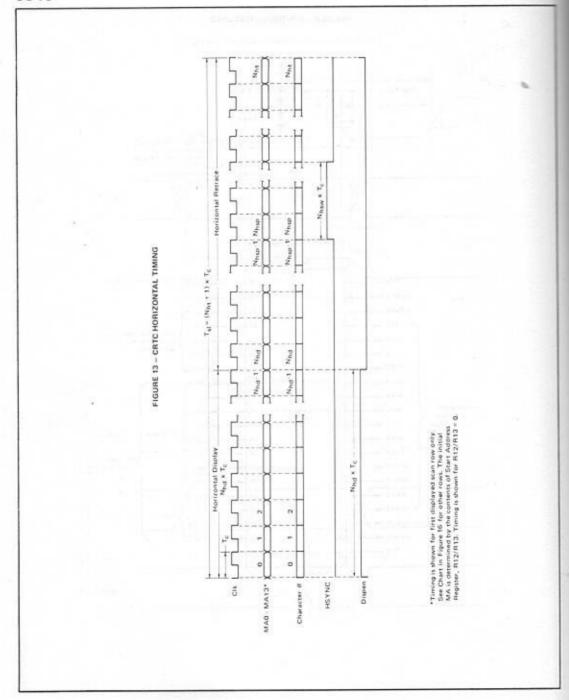

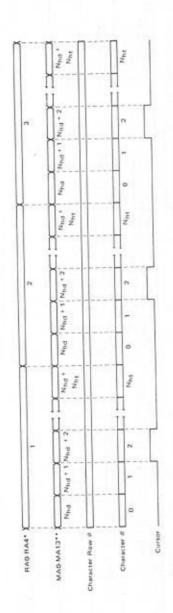

#### THE CRT TIMING CHAIN

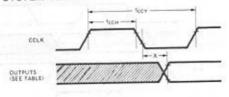

Now that we have discussed the general characteristics of a CRT display, let us look a little more closely at the timing required. Since the North American broadcast standard for television requires a horizontal synchronization (HSYNC) pulse frequency of 15.75 kHz, the deflection components of most CRT monitors are designed to operate at that frequency +5-10%. Another limiting parameter of the CRT monitors is their video response; that is, the rate at which the electron beam can be modulated. The video response range is usually much wider and therefore less limiting than the horizontal synchronization requirements. We will therefore begin our discussion of CRT timing with the horizontal synchronization requirements.

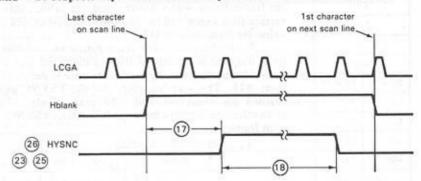

HSYNC

In the discussion that follows, you must keep in mind that the numerical values we will use, while realistic, were chosen to clarify the explanation. The actual values used will of course depend on the application and your particular requirements.

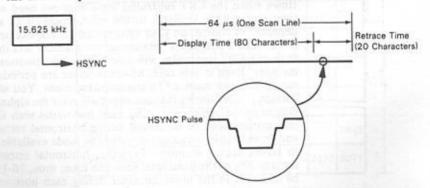

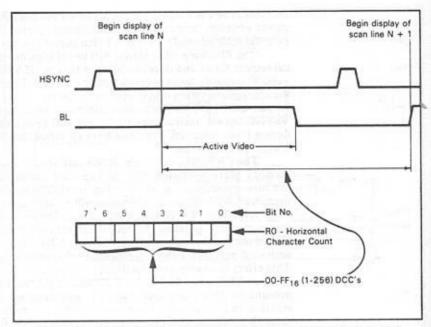

We are going to use a horizontal synchronization frequency of 15.625 kHz in our example. With this frequency, each horizontal scan line will be 64 microseconds in duration  $(1 + 15,625 = 64 \times 10^{-6})$ . The HSYNC pulse is applied to the CRT monitor electronics near the end of each horizontal scan line. Part of the 64 microseconds available for each horizontal scan line must be used for application of the HSYNC pulse and for horizontal retrace time. In a typical CRT, approximately 20% of the total horizontal scan time must be used for retrace. The relationship between the display portion of a scan line, the HSYNC pulse and retrace time can be illustrated as follows:

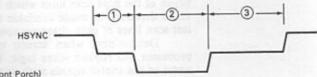

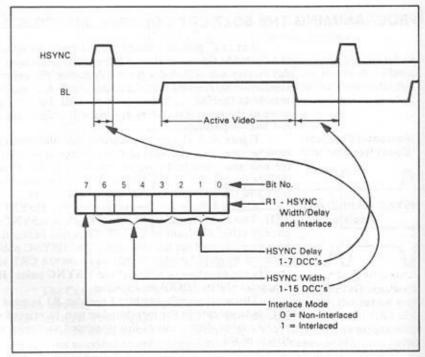

Before continuing with our description of the timing chain, let us look a bit more closely at the HSYNC signal. The horizontal retrace time can be subdivided into three intervals: the HSYNC delay, the HSYNC pulse, and the horizontal scan delay. This can be illustrated as follows:

- (1) HSYNC Delay (Front Porch)

- (2) HSYNC Pulse

- (3) Horizontal Scan Delay (Back Porch)

Front Porch Back Porch

The HSYNC delay is often referred to in television literature as the "front porch," while the horizontal scan delay is frequently referred to as the "back porch." The values for these three intervals will be determined by the operating characteristics of the CRT monitor you are using. Typical values for commercial CRT monitors would call for a total retrace time in the range of 10 to 12 microseconds and a ratio of HSYNC delay to HSYNC pulse to horizontal scan delay of 1:2:2. Thus, if we were allowing a total of 20 character times for horizontal retrace, the HSYNC delay (or front porch) would be 4 character times in duration, and the horizontal scan delay (back porch) would be 8 character times in duration. Now let us continue with our discussion of the timing chain.

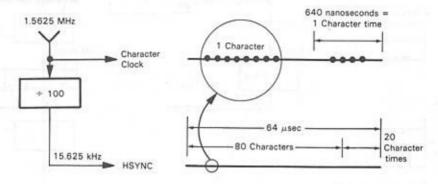

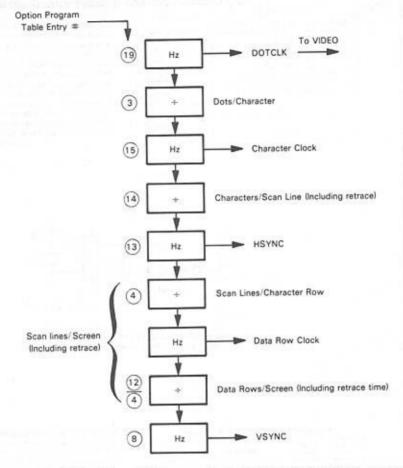

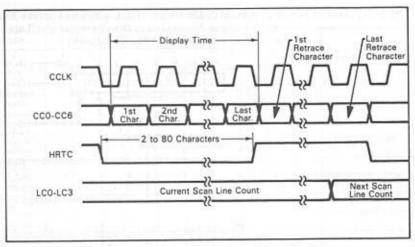

If we want to display 80 characters per line, then we must divide the available horizontal scan time into approximately 100 character-times to allow for the 20% retrace requirement. Thus the horizontal scan time for each character along a line would be 640 nanoseconds (64  $\times$  10-6  $\div$  100 = 640 $\times$ 10-9). Therefore, 640 nanoseconds of each horizontal scan line are required for each character that is to be formed. This can be illustrated as follows:

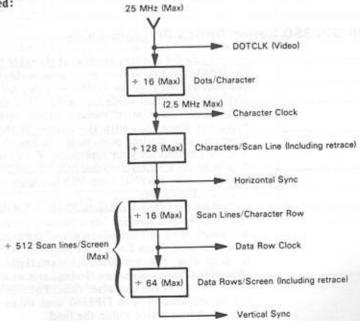

Character Clock

The 15.625 kHz frequency must be multiplied by 100 to derive the time allotted to a single character. Thus, the character clock frequency for our timing chain would be 1.5625 MHz.

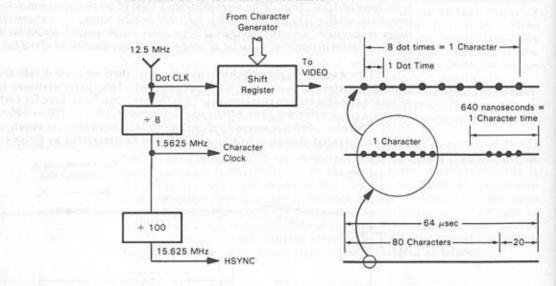

We are going to use a  $6 \times 8$  character formed in an  $8 \times 10$  matrix for this example. Each character time along the horizontal scan line must therefore be divided into 8 dot times:

Dot Clock

The dot clock that we need to clock the shift register which generates VIDEO must therefore operate at a frequency of 12.5 MHz (1.5625 imes 106 imes $8 = 12.5 \times 10^6$ ). This dot clock frequency is the highest that will be required in our system.

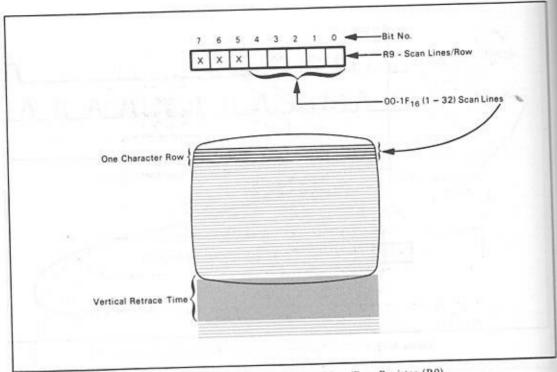

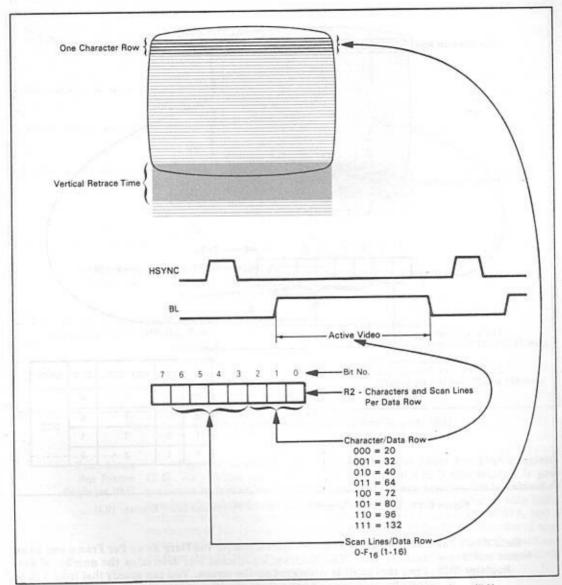

Now we have developed the timing chain from the highest frequency required down to the standard HSYNC frequency accepted by most CRT monitors. Since we have decided to use an 8 × 10 matrix to create each character on the screen, each character row will therefore require a total of 10 scan lines, or 640 microseconds including horizontal retrace time. A character or data row clock would thus run at a frequency of 1.562 kHz (15.625 kHz + 10).

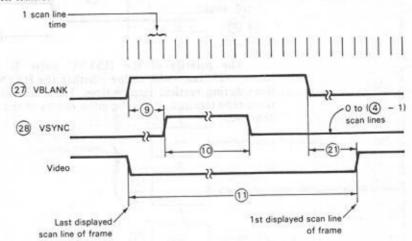

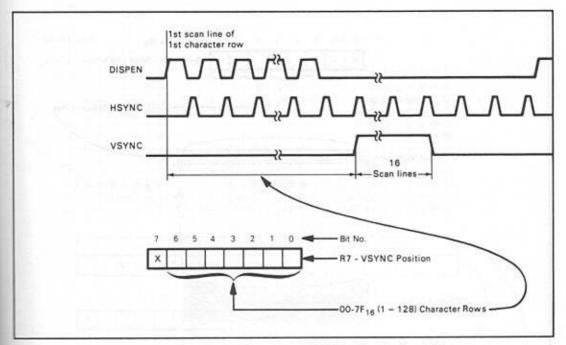

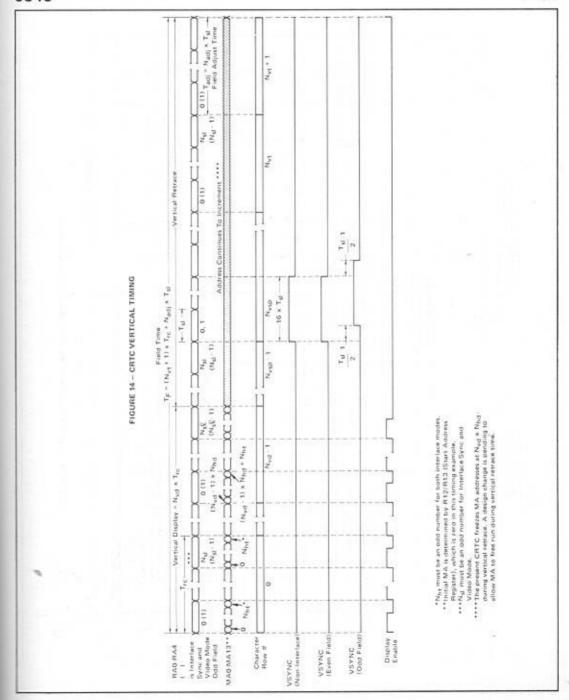

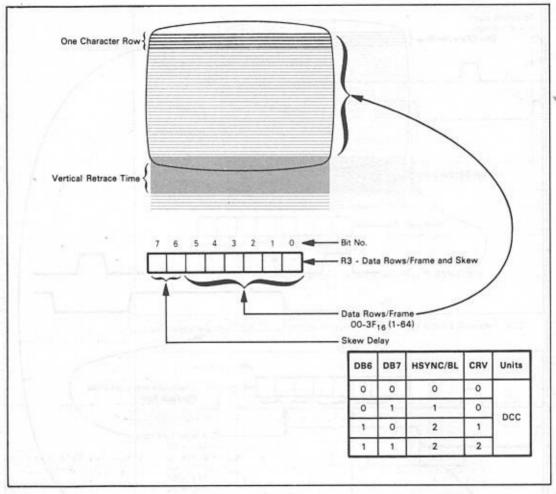

#### VSYNC

The next timing constraint we must deal with is the vertical synchronization (VSYNC) pulse used to initiate vertical retrace. You will recall that most CRT monitors in the U.S. are designed to operate with a VSYNC pulse frequency of 60 Hz. We could meet this parameter if the total number of horizontal scan lines on our screen was approximately 260 (15,625  $\div$  260 = 60.096). Thus, our display would consist of 26 character rows of 10 lines each. Of course, some time will be required for the vertical retrace operation. A typical value for this vertical retrace time might be 1 millisecond. So a period of time equivalent to 20 horizontal scan lines would give sufficient time (20  $\times$  64  $\times$  10-6 = 1.28  $\times$  10-3) for the vertical retrace. This would leave a total of 240 scan lines, or 24 character rows for display of data.

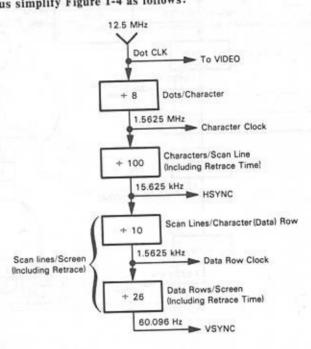

Figure 1-4 illustrates the entire timing chain that we have developed. As we mentioned at the outset, the values we have used in this example were chosen for reasons of clarity. The actual values you use will doubtless be different. To highlight some of the ways in which you can vary the timing chain, let us simplify Figure 1-4 as follows:

Figure 1-4. A CRT Timing Chain

In most applications, you will want to maintain a VSYNC frequency of 60 Hz and an HSYNC frequency that is near the commercial broadcast frequency of 15.75 kHz. Even with these constraints, however, there are still many changes we can make. For example, if we need to increase the number of characters that can be displayed on the screen we might develop the following timing chain:

In this illustration, we have increased the number of characters per line and data rows per screen by using smaller characters:  $5 \times 7$  characters in a  $7 \times 9$  matrix instead of the  $8 \times 10$  matrix of our first example. This results in a dot clock frequency that is slightly lower than that developed in our first example, and an HYSNC frequency that is somewhat higher than our previously chosen value. The HYSNC frequency is still close enough to the 15.75 kHz standard to be used with most CRT monitors, however.

### GRAPHIC VERSUS ALPHANUMERIC DISPLAYS

Most of the CRT controllers we will describe are oriented towards alphanumeric displays where data comprising a character line is repetitively presented to character generator logic until all the scan lines comprising that character row have been displayed. With this arrangement, memory storage requirements and memory accesses are minimized and the character generator logic assumes responsibility for producing each individual dot required along a scan line.

By delegating responsibility for generating each dot on the CRT screen, you have also surrendered control of each dot and are limited in what you can display by the capabilities of the character generator logic. If you wish to display graphic information in which you must have the capability of individually manipulating every dot on the CRT screen, then a different approach is required. Typically, this different approach will consume more memory and may require additional resources beyond those usually provided by a CRT controller. The concept, however, is rather straightforward. Nonetheless, we will limit our discussion of this approach since the more widespread use of the CRT controllers we describe will be in alphanumeric display applications.

Bit-Mapped Screen Memory

The most straightforward way of independently controlling every dot on the CRT screen is to map every dot to a specific memory data bit. Assuming that memory is organized as 8-bit bytes of data, you can store the dot information for eight dot locations on a scan line as one byte of memory. Thus, if the video portion of a scan line in an alphanumeric display application were used to present 80 characters, with each of them occupying seven dots along the scan line, then we could store the dot information for the scan line in 70 bytes of memory. Each 8-bit byte would be accessed from memory, loaded into a parallel-to-serial shift register, and then shifted serially at the dot clock frequency to create the CRT monitor video signal.

The memory storage requirements for a single scan line of individual dot information have not been increased beyond those required by alphanumeric data. However, while the same data stored in memory would be accessed repetitively for the 7-10 scan lines that might comprise a character row, the data for every scan line in a graphic application is unique and requires its own separate memory storage locations. If the CRT screen is to display 240 scan lines, then you must provide memory storage for 240 lines worth of dot information. In an alphanumeric application where each character row was comprised of 10 scan lines, you would only have to store 24 lines worth of data in memory.

Table 1-1 lists the CRT controller devices we will describe in this book and tabulates their salient functional capabilities.

Table 1-1. A Summary of CRT Controller Functional Characteristics

| a-u hocasius                                               | Chapter 2                           | Chapter 3                                   | Chapter 4                                                                   | Chapter 5                                                         | Chapter 6                      |

|------------------------------------------------------------|-------------------------------------|---------------------------------------------|-----------------------------------------------------------------------------|-------------------------------------------------------------------|--------------------------------|

| estitunque el sea<br>de galaciadores en                    | DP8350<br>National<br>Semiconductor | 8275<br>Intel                               | 6845<br>Motorola                                                            | 6545<br>Synertek                                                  | 5027 (9927)<br>SMC (TI)        |

| On-Chip<br>Dot Timing                                      | Yes                                 | No                                          | No                                                                          | No                                                                | No                             |

| Synchronization Signals HSYNC/VSYNC Composite Programmable | Yes<br>No<br>Yes                    | Yes<br>No                                   | Yes<br>No<br>Yes                                                            | Yes<br>No<br>Yes                                                  | Yes<br>Yes<br>Yes              |

|                                                            | 100                                 |                                             |                                                                             | 10.00                                                             |                                |

| Display Format Characters/Row Rows/Frame Scan Lines/Row    | 5-110<br>1-64<br>1-16               | 1-80<br>1-64<br>1-16                        | 1-256<br>1-128<br>1-32                                                      | 1-256<br>1-128<br>1-32                                            | 20-132*<br>1-64<br>1-16        |

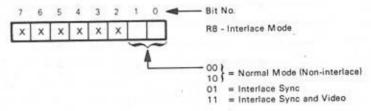

| Interlaced Mode                                            | No                                  | No                                          | Yes (2)                                                                     | Yes (2)                                                           | Yes                            |

| Cursor Mode<br>Controls                                    | Block or underline                  | Reverse video,<br>blink, underline<br>block | Reverse video,<br>blink, block,<br>underline                                | Reverse video,<br>blink, block,<br>underline                      | Block                          |

| Screen Memory<br>Addressing<br>Size (Max)                  | Linear<br>4K                        | Linear<br>64K                               | Linear<br>16K                                                               | Linear or<br>Row/Column<br>16K                                    | Row/Column<br>8K               |

| Accessible<br>Registers                                    | Cursor,<br>Top-of-Page<br>New Row   | Cursor, status,<br>light pen                | Screen format<br>and timing registers,<br>cursor, light pen,<br>Top-of-Page | Screen format<br>and timing,<br>cursor, light<br>pen, Top-of-Page | Cursor, scroll,<br>Top-of-Page |

| On-chip Buffer                                             | No                                  | Two, 80-Bytes each                          | No                                                                          | No                                                                | No                             |

| Memory Contention<br>Logic                                 | No                                  | DMA                                         | No                                                                          | Transparent<br>Memory<br>Addressing                               | No                             |

| Scrolling                                                  | Yes                                 | Yes                                         | Yes                                                                         | Yes                                                               | Yes                            |

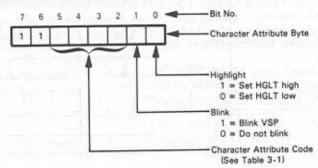

| Visual Attributes                                          | No                                  | Yes                                         | No                                                                          | No                                                                | No                             |

| Light Pen Logic                                            | No                                  | Yes                                         | Yes                                                                         | Yes                                                               | No                             |

| Process                                                    | III III III                         | NMOS                                        | NMOS                                                                        | NMOS                                                              | NMOS                           |

| Power                                                      | +5 V                                | +5 V                                        | +5 V                                                                        | +5 V                                                              | +5 V, +12 V                    |

<sup>\*</sup> Up to 200 characters/row available in mask-programmed versions.

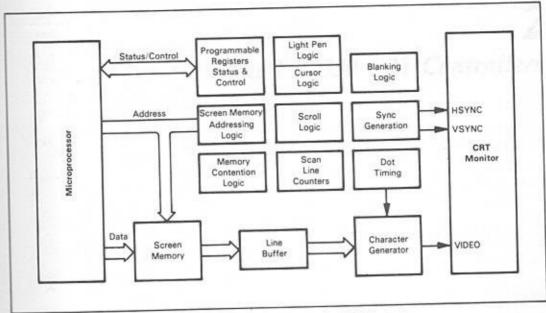

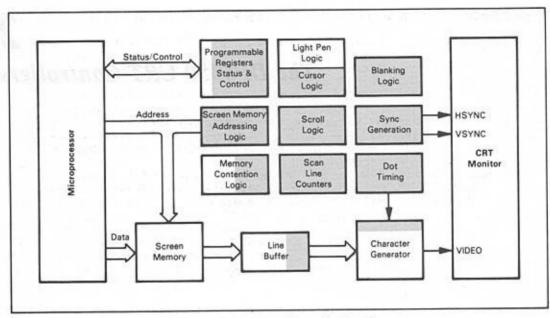

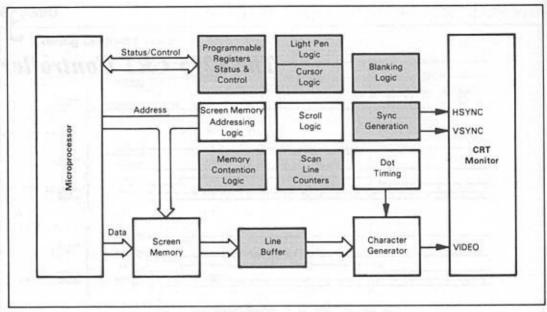

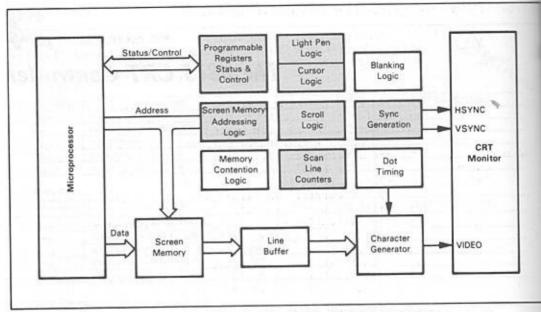

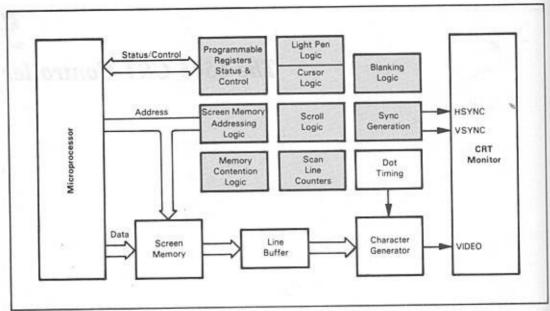

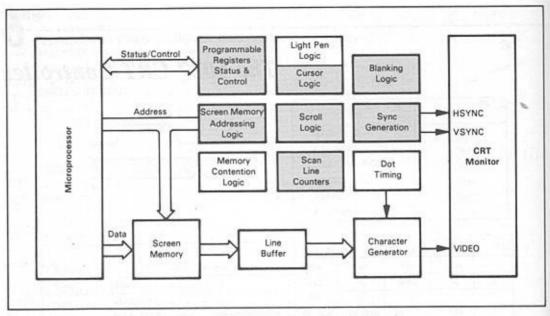

Figure 1-5. General Block Diagram of a CRT Controller

# COMPARING CRT CONTROLLER DEVICES

Figure 1-5 is a generalized block diagram showing typical logic functions that must be provided to create the interface between a microprocessor and a CRT monitor. The ideal CRT controller device would incorporate all of the logic functions shown in Figure 1-5. Actual CRT controller devices, of course, do not include all of the functional blocks illustrated - it is impossible to fit that much logic on a single chip. In addition, when you implement functions on a chip you sacrifice some flexibility: the approach that the chip designer has taken when implementing the CRT controller functions will dictate, to a large extent, the approach that you must take when incorporating the device in your system. For example, inclusion of a line buffer and the character generator logic function in Figure 1-5 implies that all CRT controllers will be used to generate alphanumeric displays. This will obviously not always be the case. This also points out one of the weaknesses of Figure 1-5: the assumptions that we have made in defining logic functions that should be included in a CRT controller. Nonetheless, we will use this illustration throughout this book to indicate the functions provided by each of the CRT controllers we will describe. While far from perfect, it does provide a starting point for comparing the capabilities of various CRT controller devices.

# The DP8350 CRT Controllers

The DP8350 CRT controller series is one of the more recently introduced set of CRT controller devices and provides some functions not available on any of the other devices described in this book. Nonetheless, because its operation is quite straightforward, we have chosen to describe the 8350 first. One reason for its relative simplicity of operation is that some of the functions which are user-programmable in other CRT controllers are mask-programmable in the DP8350s. Mask-programming of certain functions makes a great deal of sense because, while many functions need to be custom tailored to a particular design, they do not need to be altered once they have been established. The disadvantage of mask-programmable functions is, of course, that you must be a high-volume user of a particular programmed version of the DP8350 in order to justify the cost involved. If you need only a few devices and one of the standard preprogrammed versions cannot be used, you should not choose the 8350.

At this writing, the DP8350 series consists of three standard ROM versions. These are:

DP8350 80 characters/row, 24 rows, 7 × 10 field DP8352 32 characters/row, 16 rows, 9 × 12 field DP8353 80 characters/row, 25 rows, 9 × 12 field

However, an additional 15 ROM versions have been generated, some of which may be assigned standard part numbers in the future. If a low volume user cannot use one of the three standard versions, any of these non-standard versions may be used without having to pay for ROM mask development.

The largest functional difference between the DP8350s and the other CRT controllers we will describe is the inclusion of on-chip dot timing logic. The dot timing frequency is the highest that will be required in the CRT system and typically cannot be provided by an MOS device. The DP8350, however, is constructed using bipolar integrated-injected logic (I<sup>2</sup>L) technology which can provide the high speed timing.

Figure 2-1. DP8350 CRT Controller Functions

The only manufacturer of the DP8350 series is:

NATIONAL SEMICONDUCTOR CORPORATION 2900 Semiconductor Drive Santa Clara, CA 95051

Figure 2-1 illustrates those portions of the idealized CRT controller which we developed in Chapter 1 that are provided by the DP8350. Both the SYNC generation and dot timing logic are provided by the DP8350. Standard cursor and scroll logic are provided on-chip along with the screen memory addressing and scan line counter logic. The memory contention logic provided by the DP8350 is quite primitive and we have therefore shown this logic function only partially shaded. Similarly, the programmable registers provided by the 8350 are few in number, since many functions are mask-programmable. We have therefore shown this logic area as only partially present on the DP8350.

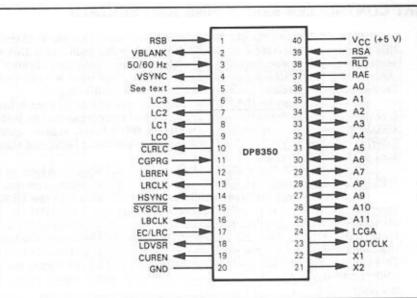

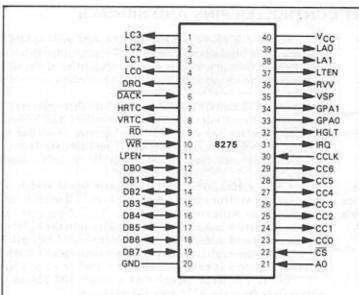

# THE DP8350 CRT CONTROLLER SERIES PINS AND SIGNALS

Figure 2-2 shows the pin assignments and signals for the DP8350. At this point we will provide a brief description of each signal, since this will serve as a good introduction to, and overview of, the capabilities of this CRT controller. Our descriptions of the signals will be brief since we will discuss their uses and interrelationship in more detail later in this chapter.

The signals may be divided into three categories: signals used to interface the CRT controller to the microprocessor and system busses (we include standard power and timing input signals in this group), signals used to interface the screen memory logic and character generator logic, and signals

sent to the CRT monitor.

Microprocessor Interface Signals

RSA and RSB are register select inputs that specify which of the DP8350's internal registers is to receive data from the microprocessor.

RLD is the register load signal used to strobe data into the DP8350 internal registers. The DP8350 registers that are accessible to the microprocessor are all write-only registers. In addition, there is no chip select input to the DP8350. Thus the RLD signal performs the functions of selecting the DP8350 device for a register load and actually strobing the data into the DP8350. Accordingly, the system logic used to generate RLD will have to combine both decoded address signals and the write signal from the microprocessor.

A0-A11 are dual purpose, bidirectional lines. They are used primarily as screen memory address output lines but they also serve as data inputs

during register load operations.

RAE is the RAM Address Enable input. In order to use the A0-A11 address lines as data input lines, the RAE signal must be set low to place the address outputs in the high-impedance mode. It is important to note that this input does not disable any of the DP8350's internal counting logic functions; it simply disables the outputs of the screen memory address lines. Thus it is up to external logic to determine whether the DP8350 will be requiring access to the address bus before the RAE input is used to disable the address outputs. We will discuss this in more detail later in this chapter.

SYSCLR is the System Clear or reset input. When you set this signal low, it clears the Cursor and Top of Page registers within the DP8350 to zero and holds the timing chain at that point where vertical and horizontal blanking

50/60 Hz. If this input is high it specifies that the CRT system refresh rate is to be 60 Hz, and if low specifies a refresh rate of 50 Hz. An interesting feature of the DP8350 is the fact that you can specify other refresh rates besides 50 and 60 Hz. The refresh rate is a mask-programmable option that you specify when you order the device. You can always specify two different frequencies for a given device. Thus, for example, you could specify a refresh rate of 37.5 Hz and 45 Hz instead of 50 Hz and 60 Hz. As part of the mask-programming specification, you assign an F1 frequency and an F0 frequency. A logic 1 input on the 50/60 Hz signal always selects the F1 refresh rate, and a logic 0 selects the Fo refresh rate.

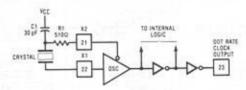

X1 and X2 are the input connections for an external, parallel resonant crystal which will determine the operating frequency for the DP8350. The crystal frequency is the dot clock rate that will be used. You can also use a system clock instead of the crystal. In this case, the dot rate clock frequency could be applied to pin 22 (X1) from a Schottky TTL series device and pin 21 (X2) should be left opened.

|                                                     | Pin Name                                                                      | Description                                                                                                                                                                                                                                              | Туре                                                                               |

|-----------------------------------------------------|-------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|

| Microprocessor System<br>Interface Signals          | RSA,RSB<br>RLD<br>SYSCLR<br>50/60 Hz<br>X1<br>X2<br>RAE<br>A0-A11<br>VCC, GND | Register Select A, B Register Load System Clear Vertical Refresh Rate Select Crystal Oscillator RAM Address Enable Register Inputs, RAM Address Outputs Power (+5 V) and Ground                                                                          | Input Input Input Input Input Input Output Input Bidirectional, Tristate           |

| Screen Memory<br>and Character Generator<br>Signals | LBCLK LBREN CGPRG LCGA LRCLK LCO-LC3 CLRLC LDVSR DOTCLK EC/LRC                | Line Buffer Clock Line Buffer Recirculate Enable Character Generator Program Latch Character Generator Address Scan Line Rate Clock Scan Line Counter Outputs Clear Line Counter Load Video Shift Register Dot Rate Clock External Clock/Line Rate Clock | Output Output Input Output Output Output Output Output Output Output Output Output |

| CRT<br>Monitor<br>Signals                           | HYSNC<br>VSYNC<br>VBLANK<br>CUREN                                             | Horizontal Synchronization<br>Vertical Synchronization<br>Vertical Blanking<br>Cursor Enable                                                                                                                                                             | Output<br>Output<br>Output<br>Output                                               |

Figure 2-2. DP8350 CRT Controller Pins and Signals

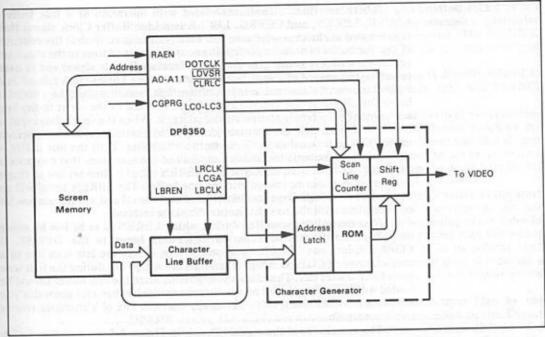

Figure 2-3. DP8350 Screen Memory and Character Generator Signals

The DOTCLK Dot Rate Clock is a buffered output at the dot rate clock frequency used for system synchronization. The positive edge of this signal should be used to clock the dot shift register.

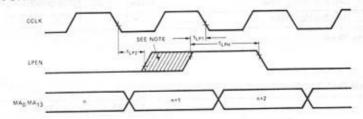

Screen Memory and Character Generator Signals

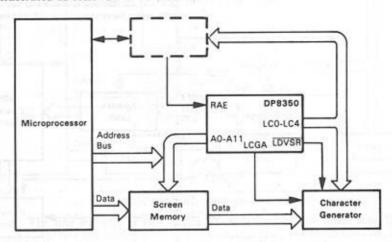

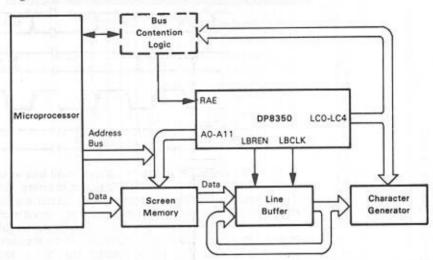

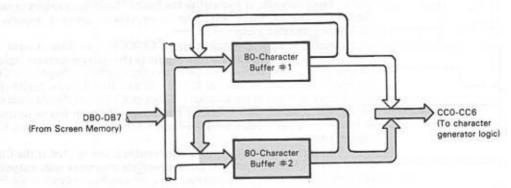

The next group of signals we shall describe are used to interface the DP8350 to screen memory and character generator logic. A subset of signals is included in this group and provides timing for a line buffer. Since the DP8350 generates the high frequency dot clock, all of these lower frequency timing signals which are derived from that clock are also generated on-chip. That is the reason for the availability of such a large number of timing signals for the character generator and line buffer logic. No other CRT controller we describe approaches the completeness of the set of timing signals provided by the DP8350. However, not all of the signals will be required in many applications since these signals imply a very specific system organization. The system organization implied by this set of signals is nearly identical to that of our idealized CRT controller. That is, an 80-character line buffer is situated between screen memory and the character generator logic as illustrated in Figure 2-3.

Screen Memory Signals

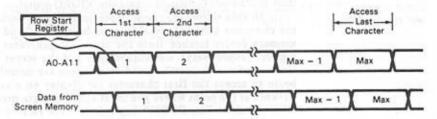

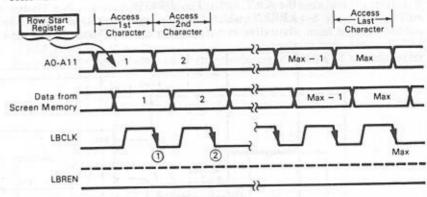

In Figure 2-3, we have shown the signals provided by the DP8350 series for interfacing to screen memory, a line buffer, and a character generator. The interface to screen memory simply consists of the 12 address outputs (A0-A11) and the related RAM Address Enable (RAE) signal which we have already discussed. The 12 screen memory address outputs allow you to have up to 4096 bytes of screen memory.

Line Buffer Signals

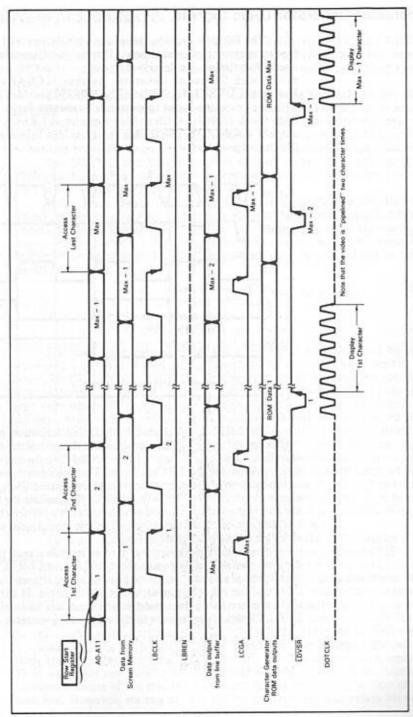

There are three signals associated with operation of a line buffer: LBCLK, LBREN, and CGPRG. LBCLK is a Line Buffer Clock signal that is generated at the character rate and which can be used to shift the contents of the line buffer in order to present the next character address to the character generator, LBREN is the Line Buffer Recirculate Enable signal and is used to select the source of input to the character line buffer. In a typical line buffer, the recirculate enable input, when high, specifies that the character being shifted out of the line buffer is also to be used as the input to the line buffer in order to simply recirculate the contents. When the recirculate input is low, it specifies that an alternate data source (in our application, screen memory) is to be used as the input to the line buffer. Thus the line buffer is shifted and its contents recirculated until all of the scan lines that comprise a character row have been displayed; the LBREN signal is then set low so that a new line of data can be loaded into the line buffer. The LBREN signal will go low at the beginning of one horizontal blanking interval and will remain low for one scan line until the next horizontal blanking interval.

You control the scan line during which LBREN is to be low by using the Character Generator Program (CGPRG) input to the DP8350. If CGPRG is low, the LBREN signal will go low during the last scan line of a character row. If CGPRG is high, then LBREN will go low during the first scan line of a character row. This allows you to select when the line buffer should be loaded with a new line, based on whether the particular character generator you are using provides blank video during the last scan line of a character row or the first scan line.

Character Generator Signals The remainder of the signals shown in Figure 2-3 are associated with the character generator function.

LCGA is the Latch Character Generator Address signal which is used to load a data word from the line buffer, or from screen memory if no line buffer was used, into the character generator address latch to select the character for display. The LCGA signal is generated at the character rate frequency.

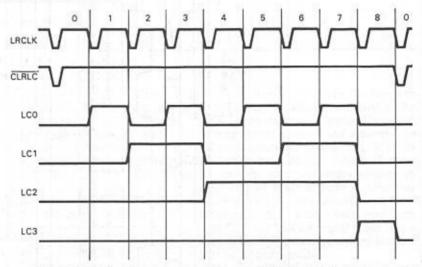

The Line Rate Clock (LRCLK) signal and the four line count output signals (LC0-LC3) are all associated with the scan line count function. The LRCLK signal is used as an input to character generators which have their own internal scan line counters to increment that internal counter as each new scan line is begun. The LC0-LC3 signal is applied to a character generator that does not have an internal scan line counter to select the proper scan line address for each character. Even if you are using a character generator with an internal scan line counter, the LC0-LC3 signals may still be of use in a system. For example, you can decode these outputs to determine the current scan line of a character row. This information might be used to grant the microprocessor access to the screen memory during non-display scan lines of a character row.

The Clear Line Counter (CLRLC) signal is generated after the last scan line of any character row to reset a scan line counter in preparation for the first scan line of a new character row. Thus if a character row consists of nine scan lines, the CLRLC signal will go low after the ninth scan line has been completed (LC3-LC0 = 1000<sub>2</sub>), resetting a character generator scan line counter to 0000<sub>2</sub>. The DP8350 will also reset its internal scan line counters at this point (LC3-LC0 = 0000<sub>2</sub>).

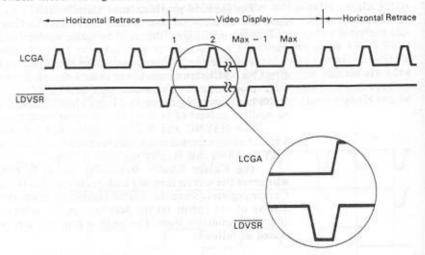

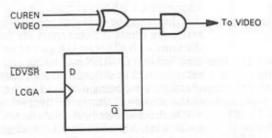

The Load Video Shift Register (LDVSR) signal is generated at the character rate and used to load a parallel dot pattern for a particular character into the parallel-to-serial converter shift register. The DOTCLK signal from the DP8350 is then used to clock the dot pattern out serially to create the VIDEO signal for the CRT monitor.

**CRT Monitor** Signals

The final group of DP8350 signals are those most directly related to the CRT monitor. There are four signals in this group: HSYNC, VSYNC, VBLANK, and CUREN.

The Horizontal Synchronization (HSYNC) and Vertical Synchronization (VSYNC) signals are the standard CRT monitor signals which we described in Chapter 1. The precise position and width of these signals and their active logic states are mask-programmable. We will describe the programming options when we discuss the programming specifications in detail later in this chapter.

The Vertical Blanking (VBLANK) signal becomes active at the start of vertical blanking - that is, upon completion of the video in the last horizontal scan line - and remains active until the beginning of the video in the first displayed scan line of the next frame. The precise scan line where the signal becomes inactive is mask-programmable, as is its polarity. The VBLANK signal may have several uses in a CRT system since it indicates a relatively long period of time when the CRT controller will not require access to the system busses.

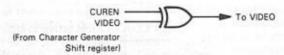

The Cursor Enable (CUREN) signal will be output high by the DP8350 during the character time that you have specified in the Cursor register. The CUREN signal will be output either on all scan lines of a character row or on a single line; you specify your choice as part of the maskprogramming procedure. Typically, the CUREN signal is logically ORed with the output of the video shift register to produce the appropriate pattern for the

cursor at the proper location on the screen.

There are two pins of the DP8350 which we have not yet discussed and whose use and purpose are rather murky. Pin 5 is shown in some of the manufacturer's literature as a pin which is not to be connected (NC) and pin 17 is given the name External Character/Line Rate Clock (EC/LRC) but is described in manufacturer's literature as a test input. Pin 5 actually performs a very specific function: if it is connected to a logic "1," then it has no effect whatsoever, but if it is connected to a low or logic "0," the number of character rows you have specified during mask-programming is cut in half. For example, if you have specified that the display is to consist of 24 character rows, then only 12 character rows will be displayed if you apply a low to pin 5. The 12 character rows will be equally spaced on the CRT screen and a full row of blanks will be interspersed between each displayed row. In addition, the screen memory address outputs will be repeated while this blank row is being displayed.

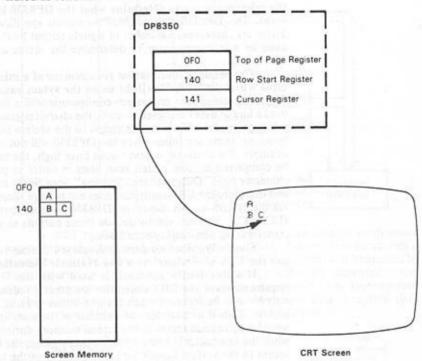

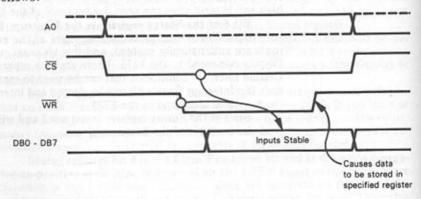

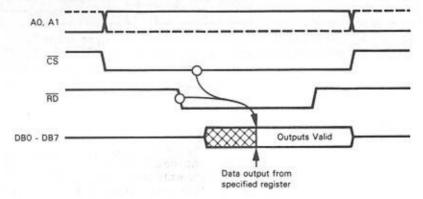

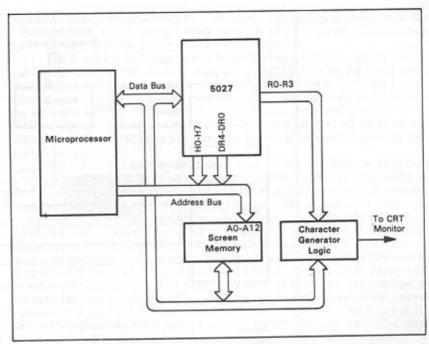

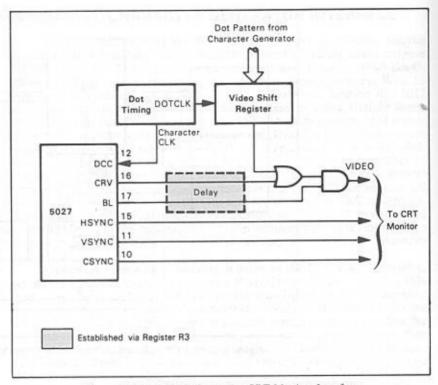

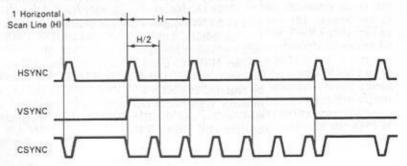

# THE DP8350 PROGRAMMABLE REGISTERS